# Slot-PLC SPC-300

# PLC - for ISA bus, integrable in every PC

| SPC-100 | Slot-PC without field bus interface |

|---------|-------------------------------------|

| SPC-200 | Slot-PC with TRS lightbus           |

| SPC-300 | Slot-PC with profibus-DP            |

| SPC-400 | Slot-PC with interbus-S             |

| SPC-410 | Slot-PC with interbus-S             |

| SPC-500 | Slot-PC with CAN - CAL              |

| SPC-510 | Slot-PC with CAN - Open             |

| SPC-520 | Slot-PC with CAN DeviceNet          |

# Software Simatic S5 (CPU 945) compatible, serial protocol AS511

Edition date/Rev. date: 27.10.1999

Document no./Rev. no.: TRS - V - BA - GB - 0094 - 04

Software version: -

File name: TRS-V-BA-GB-0094.DOC

Author: Smk / Meu

D - 78647 Trossingen Tel.: (+49) 74 25 - 2 28 - 0 Fax: (+49) 74 25 - 2 28 - 34

# <u>Imprint</u>

### TRSystemtechnik GmbH

D-78647 Trossingen Eglishalde 6

Tel.: (++49) 07425/228-0 Fax: (++49) 07425/228-34

© Copyright 1998 TRSystemtechnik

#### Guarantee

In our ongoing efforts to improve our products, TRSystemtechnik reserve the right to alter the information contained in this document without prior notice.

# **Printing**

This manual was edited using text formatting software on a DOS personal computer. The text was printed in *Arial*.

### **Fonts**

*Italics* and **bold** type are used for the title of a document or to emphasize text passages.

Passages written in Courier show text which is visible on the display as well as software menu selections.

"< >" refers to keys on your computer keyboard (e.g. <RETURN>).

# Note

Text following the "NOTE" symbol describes important features of the respective product.

# **Copyright Information ©**

MS-DOS is a registered trademark of Microsoft Corporation.

# **Revision History**

# i

# Note:

The cover of this document shows the current revision status and the corresponding date. Since each individual page has its own revision status and date in the footer, there may be different revision statuses within the document.

Document created: 25.06.1998

| Revision                                                                                                   | Date       |

|------------------------------------------------------------------------------------------------------------|------------|

| Supplementations: error table functional module, USTACK / status display, data transfer Read data block    | 12.11.1998 |

| Supplementations: programming of DB1, example DB1, error table functional module, communication via DPRAM; | 18.01.1999 |

| hardware identification replaced by component identification                                               |            |

| New: transfer of 5 data blocks in a SPS-cycle                                                              |            |

| Appendix: Various installation possibilities of a SPC                                                      | 27.10.1999 |

# **Table of contents**

| 2 Block  | ral information                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Z DIOCE  | circuit diagram                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7                    |

| 3 Views  | s of the SPC                                                                                                                                                                                                                                                                                                                                                                                                                                         | 9                    |

| 4 Starti | ing the SPC with profibus                                                                                                                                                                                                                                                                                                                                                                                                                            | 13                   |

| 5 Progi  | ramming of the real time PLC for the interbus                                                                                                                                                                                                                                                                                                                                                                                                        | 15                   |

|          | 5.1 Programming of the data block DB 1                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

|          | 5.2 Status functional module                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                   |

|          | 5.3 USTACK error messages                                                                                                                                                                                                                                                                                                                                                                                                                            | 21                   |

|          | 5.4 Communication via DPRAM                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                   |

|          | 5.5 Communication (DPRAM offset 1000H) 5.5.1 Transmission of the coupling flags 5.5.2 Transfer of a data block 5.5.3 Coupling of several SPC components 5.5.4 Status and error messages 5.5.5 Component identification 5.5.6 Transfer of 5 data blocks in a SPS-cycle  iguration of the realtime PLC  s of the SPC and their function 7.1 SPC without NPS  7.2 SPC with NPS power supply unit and accumulator 7.3 SPC with TRS NPS power supply unit | 23242526272829313232 |

|          | 7.4 Manual storage                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

| 8 Hard\  | ware description SPC base board                                                                                                                                                                                                                                                                                                                                                                                                                      | 33<br>34             |

| 8 Hardv  | ware description SPC base board                                                                                                                                                                                                                                                                                                                                                                                                                      | 33<br>34<br>34       |

| 8 Hardv  | ware description SPC base board                                                                                                                                                                                                                                                                                                                                                                                                                      | 34<br>34<br>34<br>35 |

Page 5 of 47

|              | 8.4.2.5 RUN and UPDATE switch                                                                      | 38 |

|--------------|----------------------------------------------------------------------------------------------------|----|

|              | 8.4.2.6 CMOS battery voltage                                                                       | 38 |

|              | 8.4.2.7 NPS control                                                                                |    |

|              | 8.4.2.8 NMI timer                                                                                  |    |

|              | 8.4.2.9 II/O interface                                                                             | 39 |

| 9 <b>A</b> p | pendix                                                                                             | 40 |

|              | 9.1 Pin assignments keyboard:                                                                      | 40 |

|              | 9.2 Pin assignment zero modem cable                                                                | 40 |

|              | 9.3 Wiring diagram TRS NPS power supply unit                                                       | 40 |

|              | 9.4 Various installation possibilities of a SPC                                                    |    |

|              | 9.4.1 SPC without data remanence                                                                   |    |

|              | 9.4.1.1 Standard installation                                                                      | 41 |

|              | 9.4.1.1.1 Used components:                                                                         |    |

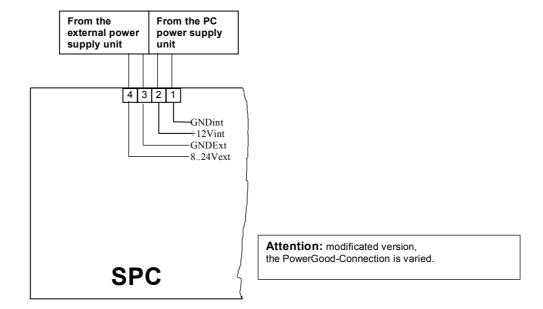

|              | 9.4.1.2 SPC in the PC with external voltage supply                                                 | 41 |

|              | 9.4.1.2.2 Used Components:                                                                         |    |

|              | 9.4.2 SPC connections with data remanence                                                          |    |

|              | 9.4.2.1 SPC in a PC with NPS power supply unit                                                     |    |

|              | 9.4.2.1.1 Used components:                                                                         | 43 |

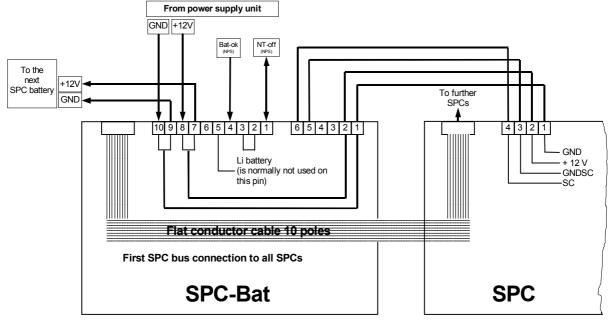

|              | 9.4.2.2 Several SPCs in a PC with NPS power supply unit                                            |    |

|              | 9.4.2.2.1 Used components:                                                                         |    |

|              | 9.4.2.3 SPC with data remanence                                                                    |    |

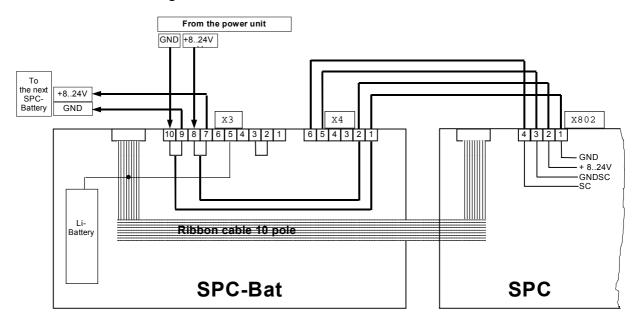

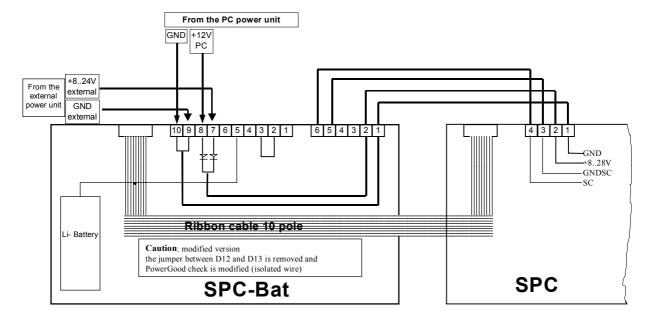

|              | 9.4.2.3.1 Connection diagram                                                                       |    |

|              | 9.4.2.3.2 Used components:9.4.2.4 SPC with data remanence and additional external power supply     |    |

|              | 9.4.2.4 SPC with data remainence and additional external power supply 9.4.2.4.1 Connection diagram |    |

|              | 9.4.2.4.2 Used components:                                                                         |    |

|              | 9.4.2.5 General installation notes                                                                 |    |

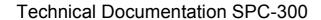

# 1 General information

- The SPC component is a PLC (Programmable Logical Control), which can be integrated in any PC.

- The PLC communicates with the higer-level host PC via a dual-ported RAM. In this dual-ported RAM, the process image is provided.

- One of the two serial interfaces of the SPC is used for programming the PLC. This offers the possibility to program the PLC not only with the host PC, but also by means of an external laptop or a Siemens programmer. The AS511 (optionally an IBH Softec protocol as well) is used as a protocol at the serial interface.

- The PLC disposes of the capacity range of a SIEMENS 945 CPU, regarding the command set.

Date: 27.10.1999 TRS - V - BA - GB - 0094 - 04 Page 6 of 47

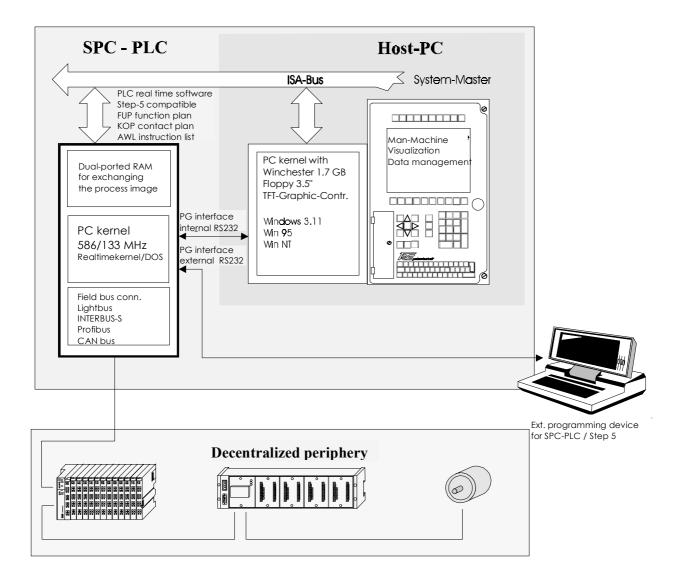

# 2 Block circuit diagram

# The SPC consists of several components

A base board containing the following components.

- a) 8 KB dual-ported RAM for communication with the ISA bus

- b) Two PC-104 slots

- c) Plug for two serial interfaces

- d) Integrated lightbus connection

- e) Integrated CAN bus connection

- f) Interface to an NPS power supply unit

- g) Parallel interface for offset switches and display

- h) 7-segment displays for displaying the status

- i) Switch for Run/Stop

- j) Switch for normal/special operation

- k) Key for Reset

- I) Key for Load

- m) 4 MB FLASH EPROM

- n) Optionally up to 1 MB SRAM

A PC (IBM-compatible) which is plugged in either of the two PC-104 slots and which contains the following components.

- a) CPU 586 / 133 MHz

- b) 4 MB RAM (extensible)

- c) 800 KB Flash Eprom as drive "C:"

- d) 4 MB Flash Eprom as drive "D:" (extensible)

- e) Two serial interfaces COM 1 and COM 2

- f) One parallel interface

- g) Connection for floppy drive

- h) Connection for keyboard

A second PC-104 slot which can be used for expansion boards.

- a) Profibus DP connection

- b) Interbus-S connection

- c) CAN bus connection (unless the integrated one is used)

- d) Any other boards such as VGA controller, etc.

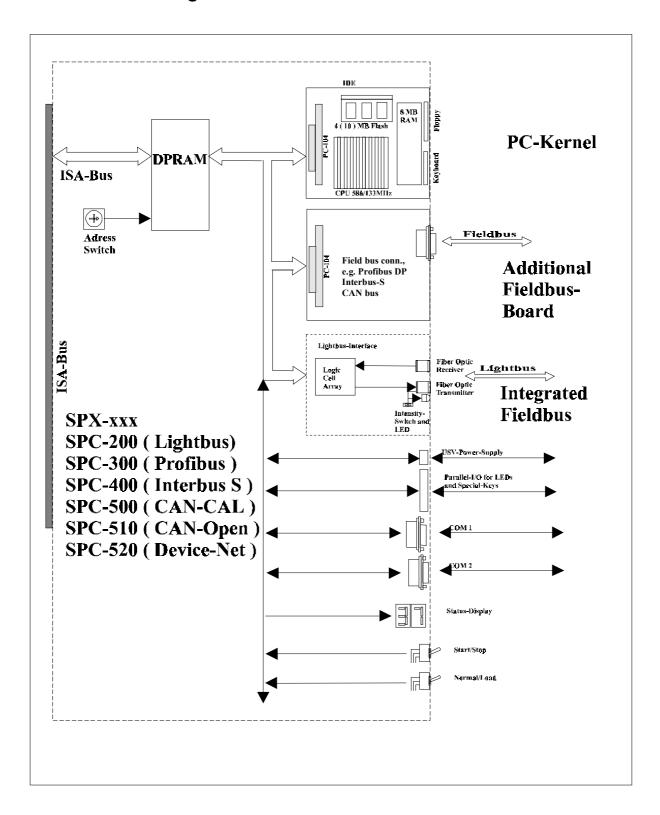

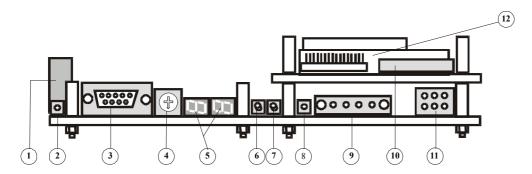

# 3 Views of the SPC

# Top view:

### Front view:

- Serial interface COM 1

- Reset key

- 2 Serial interface COM 2

- 4 Address setting segment address dual-ported RAM

- 5 Status display

- 6 RUN/STOP PLC switch

- PLC mode / Interlink mode switch

- 7 Reload Flash key

- Plug for external voltage supply 9

- 10 Connection for floppy drive

- Interface NPS (Non-interrupted power supply) 11

- 12 PC kernel based on PC-104, CPU 586/133MHz with Flash

- 13 Intensity switch for lightbus

- Intensity display 14

- PC-104 plug for field bus connections such as Profibus DP, Interbus-S, CAN bus 15a

- 15b PC-104 plug for PC kernel

- 16 Connection for ext. keyboard

- Balancing of transmitting power for lightbus 17

- 18 Connection for hard disk or flash disk

# 1 Serial interface COM 1

Either laptop or Siemens PG.

In the interlink mode, COM 1 can be used for updating the firmware or for modifying the initialization files.

# 2 Reset key

With this key, the PLC-CPU can be reset.

### 3 Serial interface COM 2

In the PLC mode, an external programmer can also be connected to COM 2. Either laptop or Siemens PG.

In the interlink mode, COM 2 can also be used for updating the firmware or for modifying the initialization files.

# 4 Address setting segment address dual-ported RAM

The basic address of the dual-ported RAM is set here. The size of the dual-ported RAM is 8 KB.

| Switch position | Segment address |

|-----------------|-----------------|

| 0               | 0D000H          |

| 1               | 0D200H          |

| 2               | 0D400H          |

| 3               | 0D600H          |

| 4               | 0D800H          |

| 5               | 0DA00H          |

| 6               | 0DC00H          |

| 7               | 0DE00H          |

# **Default setting**

# 5 Status display

The status display is a 2-digit 7-segment display indicating the status of the PLC or error messages

| Display | Signification |

|---------|---------------|

| 1       | PLC = RUN     |

| 0       | PLC = STOP    |

In case of error messages, the display flashes. The error messages are explained in Chapter 5 Error messages.

# 6 RUN/STOP PLC switch

This key starts or stops the PLC.

| Position | Signification |

|----------|---------------|

| Left     | PLC = RUN     |

| Right    | PLC = STOP    |

Position left signifies that the switch points away from the base board. Position right signifies that the switch points towards the base board.

# 7 PLC mode / Interlink mode switch

This switch has several functions. On switching on the SPC component, the position of this switch decides whether the component starts in PLC mode or in interlink mode.

| Position | Signification  |

|----------|----------------|

| Left     | PLC mode       |

| Right    | Interlink mode |

In the interlink mode, either the firmware can be updated or the initialization files can be modified.

In the PLC mode, this switch allows to store the current PLC program from the RAM in the Flash Eprom or in the SRAM. During storage, the flashing value "80" is shown in the status display. After completion of storage, the status display indicates an "0" = current PLC Stop.

| Position | Signification     |

|----------|-------------------|

| Left     | PLC mode          |

| Right    | Store PLC program |

In order to switch over between PLC mode and interlink mode or vice versa, first press the RESET key, then change the switch position.

**ATTENTION:** If switching is accidentally performed in the PLC mode first, wait until storage

is completed before pressing the RESET key

(status display = "0"), since the PLC program may be destroyed during

storage.

# 8 Reload Flash key

When using the TRS NPS power supply unit, the Reload Flash key allows to reload the PLC program from the flash disk if it should have got lost in the SRAM.

# 9 Plug for external voltage supply

If the SPC is operated outside a PC, or if a power supply unit board with TRS NPS power supply unit is used, the supply voltage is connected via this plug.

# 10 Connection for floppy drive

Using a special cable, a floppy drive can be connected to the PC kernel.

### 11 Interface NPS (Non-interrupted Power Supply)

A flash or a battery-buffered SRAM serves for storing remanent flags and data blocks. The power supply unit generates a signal indicating to the PC kernel that the power supply has broken down. Now the CPU stores in the flash or in the SRAM and then switches off the NPS supply.

### 12 PC kernel based on PC-104, CPU 586/133MHz

# 13 Intensity switch for lightbus

The intensity of the OWG transmitter can be modified via the switch. If the LED display Intensity is flasing, transmission is performed with high intensity. When using OWG cables shorter than 15m, low intensity should be activated. In this case, the LED display Intensity is dark.

# 14 Display Intensity

| LED ON  | High intensity for cable lengths > 10 m    |  |

|---------|--------------------------------------------|--|

| LED OFF | Lowered intensity for cable lengths < 10 m |  |

# 15a PC-104 plug for expansion boards

Any PC-104 modules can be plugged on this plug. Field bus connections such as profibus DP, interbus-S or CAN bus are plugged here.

# 15b PC-104 plug for PC kernel

# 16 Connection for ext. Keyboard

An ext. keyboard can be connected to the PC kernel. Thus, together with a VGA board, a PC kernel can become a complete PC.

# 17 Balancing of transmitting power for lightbus

The transmitting power (intensity) of the lightbus interface is balanced at the factory.

# 18 Connection for hard disk or flash disk

Using a special cable, a hard disk can be connected to the PC kernel. In delivery state, a flash disk is attached to this connection.

# 4 Starting the SPC with profibus

- 1. Make sure that the address range D000H up to D1FFH in your PC is free (default setting on delivery). If this address range is already occupied, choose another address range using the switch for address setting of the segment address.

- 2. Plug the SPC in a vacant ISA slot in your PC.

- 3. Now switch on your PC. If the PLC mode / interlink mode switch is in PLC mode position, a flashing error message is shown in the status display after booting the SPC. This error message only indicates that no PLC program has been transmitted to the SPC yet.

- 4. Now install the system configurator for the profibus on your host PC or an external programmer you can find on the enclosed CD. The "Device driver" on the system configurator CD "does not have to be installed" as it is only necessary for the configuration of ISA bus master components. For the SPC, configuration is performed via the serial interface. In order to operate the system configurator, refer to a manual on the CD you can find in the subdirectory MANUALS. The manual is stored as a PDF file and can be read and printed using the ACROBAT Reader.

- 5. Now the profibus master component must be parameterized using the system configurator. This signifies that the master component is informed about the users connected to the profibus and about the I/O addresses where they have to store their data. The system configurator to be found on the host PC or an external programmer must be connected with the profibus master component via a zero modem cable. The parameterized interface is located on the slot plate which is connected with the SPC by the two flat conductor cables. The lower sub D plug is for parametering, the upper sub D plug is for the profibus.

- 6. When the parameterization of the profibus master component is completed, connect COM 1 of the SPC with your host PC, or with the external programmer thus you can start programming the PLC program. As default, the SPC is adjusted to the Siemens AS-511 serial protocol.

- 7. Now you can start programming the PLC program. If you use the programming software "S5W" by IBH-Softec for programming, adjust in the menu "Project" as interface, COM 1 or COM 2, and as appliance Siemens PLC (AS511).

If you use a Siemens programmer or another programming software, make sure that a corresponding setting is performed.

- 8. The profibus PLC disposes of a firmly programmed status module (default FB 10). If you do not agree with the status FB number = 10, change it as follows:

The file "PBSDRV.INI" is located in the path "PLC43" in drive "D:" of the SPC. In this file, the number of the status functional module is defined. If you wish to change it now, create an interlink connection to your host PC or a programmer. This is necessary as otherwise an access to the drives of the SPC is not possible. The interlink connection is performed via the serial interface. Thus you can use the serial cable of the programmer (zero modem cable).

To create an interlink connection, insert the following line into the file "CONFIG.SYS" on your host PC and reboot the latter:

DEVICE=C:\DOS\INTERLNK.EXE /COM:1 /DRIVES:4 /NOPRINTER /NOSCAN

If you use COM 2 on your host PC, insert /COM:2.

Now switch the SPC to the interlink mode by pressing the Reset key and then turning the "PLC mode / Interlink mode" to the right into the position "Interlink mode". The SPC reboots and provides its drives to the host PC via interlink. Now you can edit the file PBSDRV.INI with an editor. Regarding the signification the entries, refer to the chapter "Configuration of the real time PLC". After completion of the modifications, switch back the SPC to the PLC mode by pressing the Reset key and then turning the "PLC mode / Interlink mode" switch to the left into the position "PLC mode". The SPC then reboots.

# **Technical Documentation SPC-300**

- 9. Now start the programming interface, e.g. S5W by IBHSoftec. Click on the icon PLC module directory. The lower status line indicates the serial transmission of the OBs, PBs, FBs etc.

- 10. Now start your PLC program by turning the RUN / STOP switch to the right (Stop PLC) and back again to the left (RUN-PLC). If the PLC program is perfect, the status display indicates with a 1 that the PLC runs. If the status display indicates an 0, the PLC is in STOP.

- 11. Now the PLC program is stored in the RAM memory of the SPC. In order that the program will still be available after connecting and disconnecting the supply voltage of the SPC, you have to store it in the flash of the SPC turning the switch "PLC mode / Interlink mode" to the right into the mode "PLC program store". Now the SPC indicates by a flashing 80 in the status display that the data will be stored. The end of storage is displayed by an 0 in the status display which no longer flashes. During storage, the PLC is set to stop and must be restarted with the RUN / STOP switch afterwards.

Date: 27.10.1999 TRS - V - BA - GB - 0094 - 04 Page 14 of 47

# 5 Programming of the real time PLC for the interbus

# 5.1 Programming of the data block DB 1

The data block DB1 is used for parameterizing the SPC from the PLC program. In contrast to the file PBSDRV.INI where parameters are firmly set, DB 1 allows to modify parameters during PLC programming as well. Make sure that the PLC program is restarted when values are modified in the DB1, since the modified values are only activated after a STOP/RUN.

The DB1 is divided in 8 data blocks which are explained below. The first data word of the data blocks 2 - 8 contains a detection CODE which determines the function that is executed by this data block. The further data words of a data block are parameters of the individual functions. The sequence of the data blocks 2 - 8 is optional. Data block 1 contains a header identifying the DB1 as parameterization DB. The end of the DB1 is defined by the end identification. If the data block DB1 is not programmed, or if there is no header, none of the functions for the blocks 2 - 8 is executed. If individual blocks are not defined, only the functions of these blocks are not executed.

If the DB1 is not available, if faulty entries have been found in the DB1, or if there is no end identification, an error message is generated which is output in the status functional module in the parameter **ERN**.

#### Block 1: Header:

The first 3 data words of the DB1 contain the ASCII code for the string "MASK01"

KH = 4D41 "MA" KH = 534B "SK" KH = 3031 "01"

If there is no header, the DB1 is not accepted as parameterization DB, and none of the following blocks has a function.

### **Block 2:** Code CE00 = Coupling flag inputs:

Coupling flag inputs define the flags which are copied from the flag range of the PLC to the DPRAM and thus are provided for visualization. The start flag and the numbers of flags to be transmitted are defined as parameters. The start flag must be within the range of 0 to 255. The number must be selected in such a way that the addition Start flag + Number does not exceed the value 256. If these two conditions are not fulfilled, an error message will be caused.

#### **Block 3:** Code CA00 = Coupling flag outputs:

The coupling flags outputs allow a visualization to modify the flags in the flag range of the PLC. For this, it writes the data for the flags in the DPRAM from where they are read by the PLC. The start flag and the numbers of flags to be transmitted are defined as parameters. The start flag must be within the range of 0 to 255. The number must be selected in such a way that the addition Start flag + Number does not exceed the value 256. If these two conditions are not fulfilled, an error message will be caused.

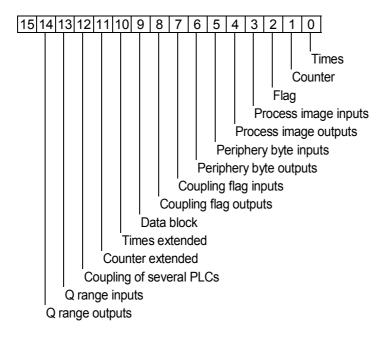

#### **Block 4:** Code CC00 = Release DPRAM update:

The parameter of this block determines the data (times, counters, flags etc.) which are written in the DPRAM or read from there. Setting individual bits in this parameter releases the update of the required data. If individual ranges are not selected, the PLC program is processed faster.

# **Block 5:** Code CB00 = Remanent flags:

Definition which flags of the flag range of the PLC shall keep their data after disabling and reactivating the voltage supply. The start flag and the numbers of flags to be remanent are defined as parameters. The start flag must be within the range of 0 to 255. The number must be selected in such a way that the addition Start flag + Number does not exceed the value 256. If these two conditions are not fulfilled, an error message will be caused.

### **Block 6:** Code CB01 = Remanent S flags:

Definition which S flags of the flag range of the PLC shall keep their data after disabling and re-activating the voltage supply. The start flag and the numbers of flags to be remanent are defined as parameters. The start flag must be within the range of 0 to 4095. The number must be selected in such a way that the addition Start flag + Number does not exceed the value 4096. If these two conditions are not fulfilled, an error message will be caused.

#### **Block 7:** Code CB02 = Remanent counters:

Definition which counters of the flag range of the PLC shall keep their data after disabling and reactivating the voltage supply. The start counter and the numbers of counters to be remanent are defined as parameters. The start counter must be within the range of 0 to 255. The number must be selected in such a way that the addition Start flag + Number does not exceed the value 256. If these two conditions are not fulfilled, an error message will be caused.

#### **Block 8:** Code CD00 = Coupling of several PLCs:

If several SPCs are available in a computer system, it is possible to exchange data between the individual SPCs via the visualization (see chapter "Coupling of several SPC components").

First parameter = data block no.

Second parameter = number of PLCs max. 7

Third parameter = block length of the range max. 32 words

End EEEE<sub>H</sub> identifi-cation

TR - Systemtechnik GmbH, Eglishalde 6, 78647 Trossingen, Tel. +49 - (0) 7425-228-0, Fax +49 - (0) 7425-228-34

# 5.1.1 Example data block DB1

| DW | 0:<br>1:<br>2: | KH = 534B                                      | Header 3 words<br>(MASK01)                                                                                                                                                   |

|----|----------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DW | 3:<br>4:<br>5: | KH = CE00<br>KF = + 0<br>KF = + 256            | Coupling flag inputs PLC -> visualization<br>First entry start flag<br>Second entry = number                                                                                 |

| DW | 6:<br>7:<br>8: | KH = CA00<br>KF = + 0<br>KF = + 256            | Coupling flag outputs visualization -> PLC First entry start flag Second entry = number                                                                                      |

| DW | 9:<br>10:      | KH = CC00<br>KH = 7FFF                         | Release DPRAM update                                                                                                                                                         |

| DW |                | KH = CB00<br>KF = + 50<br>KF = + 10            | Definition of the remanent flags to be stored<br>First entry start flag<br>Second entry = number                                                                             |

| DW | 15:            | KH = CB01<br>KF = + 0<br>KF = + 4096           | Definition of the remanent S flags to be stored<br>First entry start flag<br>Second entry = number                                                                           |

| DW |                | KH = CB02<br>KF = + 0<br>KF = + 4096           | Definition of the remanent counters to be stored<br>First entry start counter<br>Second entry = number                                                                       |

| DW | 22:            | KH = CD00<br>KF = + 9<br>KF = + 7<br>KF = + 32 | Definition of the data coupling between several PLCs First entry = data block no. Second entry = number of PLCs max. 7 Third entry = block length of the range max. 32 words |

| DW | 24:            | KH = EEEE                                      | End identification                                                                                                                                                           |

### 5.2 Status functional module

For status and error messages which do not result in a stop of the PLC, a firmly installed functional module is available. The FB used for this is determined in the file PBSDRV.INI. This functional module has 7 parameters.

**CTR: Control Byte:** If the 1st bit is set in the control byte, the profibus master board is induced to restart the interbus. When the restart has been performed, this bit must be reset.

**STA:** Status Byte: If the restart of the profibus requested in the control byte has been performed, this is acknowledged in the status byte by setting the 1st bit. If the 1st bit of the control byte is reset afterwards, the 1st bit in the status byte is reset as well.

**ENR:** Error No.: Provides the error number of the occurred error (see table below).

**ERC:** Extended Error Code: Provides an extended error description (see table below).

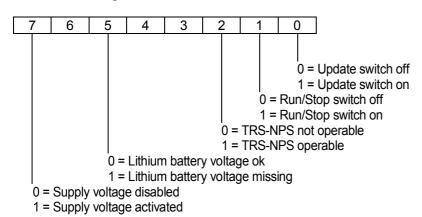

SPC Status Register SPC Hardware

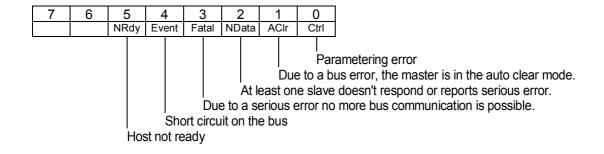

PB1: Diagnosis register 1 of the profibus master component

PB2: Diagnosis register 2 of the profibus master component

### ENR, ERC: Error table Functional module Error messages:

| Error | Extended   | Description                                                               |

|-------|------------|---------------------------------------------------------------------------|

| Code  | error code | ·                                                                         |

| ENR   | ERC        |                                                                           |

| 1     |            | Data block DB1 not found                                                  |

| 2     |            | Data block DB1 empty                                                      |

| 3     |            | Wrong header in DB1                                                       |

| 4     |            | DB 1 contains too few parameters or parameters which are not in the valid |

|       |            | range.                                                                    |

| 5     |            | End identification in DB1 not found                                       |

| 6     | DB No.     | Data block for reading data not found (DB)                                |

| 7     |            | Offset of the data to be read too big (DB)                                |

| 8     |            | Number of the data to be read too high (DB)                               |

| 9     | DB No.     | Data block for writing data not found (DB)                                |

| 10    |            | Offset of the data to be written too big (DB)                             |

| 11    |            | Number of the data to be written too high (DB)                            |

| 16    |            | Number of the data block to the SPC coupling too high                     |

| 17    |            | Number of input ranges too high                                           |

| 18    |            | Number of data words too high                                             |

| 19    |            | Data block with stated number does not exist                              |

| 20    |            | Length of the data block too low                                          |

| 21    | DB No.     | Data block for reading data not found (DX)                                |

| 22    |            | Offset of the data to be read too big (DX)                                |

| 23    |            | Number of the data to be read too high (DX)                               |

| 24    | DB No.     | Data block for writing data not found (DX)                                |

| Error<br>Code | Extended error code | Description                                                                                         |

|---------------|---------------------|-----------------------------------------------------------------------------------------------------|

| ENR           | ERC                 |                                                                                                     |

| 25            |                     | Offset of the data to be written too big (DX)                                                       |

| 26            |                     | Number of the data to be written too high (DX)a                                                     |

| 30            |                     | File PLC43SPC.BIN could not be opened for storage (Step 5 program file).                            |

| 31            |                     | Error in writing in the Step 5 program file PLC43SPC.BIN                                            |

| 40            |                     | Profibus master not ready for warm boot (Ready bit = 0).                                            |

| 41            |                     | Profibus master does not acknowledge the warm boot request within prescribed time (Init bit not 0). |

| 42            |                     | Profibus master does not acknowledge Ready bit within prescribed time                               |

| 43            |                     | Profibus master does not acknowledge Run bit within prescribed time                                 |

| 44            |                     | Profibus master does not acknowledge Com bit within prescribed time                                 |

# **SPC: Status Register SPC Hardware**

# PB1: Low byte diagnosis register 1 of the profibus master component

# PB1: High byte diagnosis register 1 of the profibus master component

This byte represents the main status of the master.

Bit = 1: Data cycles on the profibus are carried out (profibus works)

Bit = 1: Profibus initialization has been carried out

Bit = 1: Firmware of the master component has started correctly

# PB2: Low byte diagnosis register 2 of the profibus master component

The following error messages are output if the value 255 is set in the high byte of the diagnosis register 2.

| Error | Description                                                        | Error source  |

|-------|--------------------------------------------------------------------|---------------|

| Code  |                                                                    |               |

| 50    | USR-INTF-task not found                                            | Master        |

| 51    | No global data field                                               | Master        |

| 52    | FDL-task not found                                                 | Master        |

| 53    | PLC-task not found                                                 | Master        |

| 54    | Master parameters don't exist                                      | Master        |

| 55    | Defective value in the master parameters                           | Configuration |

| 56    | Slave parameters don't exist                                       | Configuration |

| 57    | Defective value in the slave parameters                            | Configuration |

| 58    | Double slave address                                               | Configuration |

| 59    | One user has a parameterized offset address of the sending process | Configuration |

|       | data that is beyond the allowed limit of 0 – 255                   |               |

| 60    | One user has a parameterized offset address of the receiving       | Configuration |

|       | process data that is beyond the allowed limit of 0 – 255           |               |

| 61    | Data range of the slaves overlaps into the sending process data    | Configuration |

| 62    | Data range of the slaves overlaps into the receiving process data  | Configuration |

| 63    | Unknown process data handshake                                     | Warm boot     |

| 64    | No more RAM memory available                                       | Master        |

| 65    | Defective slave parameter data                                     | Configuration |

| 202   | No vacant segment for processing                                   | Master        |

| 212   | Error when reading parameter data base                             | Master        |

| 213   | Error when transferring structure to operating system              | Master        |

The following error messages are output if a value unequal to 255 is set in the high byte of the diagnosis register 2.

| Error | Description                                                    | Error source    |

|-------|----------------------------------------------------------------|-----------------|

| Code  |                                                                |                 |

| 2     | User signals overflow                                          | Master telegram |

| 3     | Request function of the master is not activated in the station | Master telegram |

| 9     | No response data, although the slave must respond with data    | Slave           |

| 17    | No reaction of the station                                     | Slave           |

| 18    | Master is not in the logic token ring                          | Master          |

# PB2: Diagnosis register 2 high byte of the profibus master component)

This byte contains the module number of the bus user if an error has occurred. If the error has occurred within the master, not on the bus, this byte contains the value 255.

# 5.3 USTACK error messages

Error messages which cause a stop of the PLC, are indicated in the USTACK and on the SPC display. The USTACK can be read with the PLC-programmer.

# Error messages in the USTACK and in the status display

| Error           | Extended   | Description                                                              |

|-----------------|------------|--------------------------------------------------------------------------|

| Code            | error code |                                                                          |

| E1 <sub>H</sub> |            | File PLC43SPC.BIN could not be opened for loading (Step 5 program file). |

| E2 <sub>H</sub> |            | Error on reading from the Step 5 program file PLC43SPC.BIN               |

| E3 <sub>H</sub> |            | Checksum error on reading the Step 5 program from the file PLC43SPC.BIN  |

| E4 <sub>H</sub> |            | Step 5 program does not exist in the SRAM memory.                        |

| E5 <sub>H</sub> |            | Checksum error on reading the Step 5 program from the SRAM memory.       |

| E6 <sub>H</sub> |            | Profibus master component not found (No hardware identification).        |

| E7 <sub>H</sub> |            | Profibus master component not operative after reset.                     |

| FF <sub>H</sub> |            | Temporary voltage loss                                                   |

# 5.4 Communication via DPRAM

# **Division of the DPRAM for communication with a visualization CPU**

| DPRAM<br>OFFSET   |                                               |            | Number of bytes |

|-------------------|-----------------------------------------------|------------|-----------------|

| 0 <sub>H</sub>    | Times                                         | READ       | 256             |

| 100 <sub>H</sub>  | Counter                                       | READ       | 256             |

| 200 <sub>H</sub>  | Flag                                          | READ       | 256             |

| 300 <sub>H</sub>  | Process image inputs                          | READ       | 128             |

| 380 <sub>H</sub>  | Process image outputs                         | READ       | 128             |

| 400 <sub>H</sub>  | Periphery byte inputs                         | READ       | 128             |

| 480н              | Periphery byte outputs                        | READ       | 128             |

| 500 <sub>H</sub>  | Coupling flag inputs                          | READ       | 256             |

| 600 <sub>H</sub>  | Coupling flag outputs                         | WRITE      | 256             |

| 700 <sub>H</sub>  | Data range Read data block                    | READ       | 512             |

| 900 <sub>H</sub>  | Data range Write data block                   | WRITE      | 512             |

| В00н              | Times extended                                | READ       | 256             |

| С00н              | Counter extended                              | READ       | 256             |

| D00 <sub>H</sub>  | Q range inputs                                | READ       | 256             |

| Е00н              | Q range outputs                               | READ       | 256             |

|                   |                                               |            |                 |

| 1000 <sub>H</sub> | Communication                                 | READ/WRITE |                 |

| 1100 <sub>H</sub> | SPC coupling output data                      | READ       | 64              |

| 1140 <sub>H</sub> | SPC coupling input data 1                     | READ       | 64              |

| 1180 <sub>H</sub> | SPC coupling input data 2                     | READ       | 64              |

| 11C0 <sub>H</sub> | SPC coupling input data 3                     | READ       | 64              |

| 1200 <sub>H</sub> | SPC coupling input data 4                     | READ       | 64              |

| 1240 <sub>H</sub> | SPC coupling input data 5                     | READ       | 64              |

| 1280 <sub>H</sub> | SPC coupling input data 6                     | READ       | 64              |

| 12C0 <sub>H</sub> | SPC coupling input data 7                     | READ       | 64              |

|                   |                                               |            |                 |

| 1300 <sub>H</sub> | Fast transfer of 5 data blocks in a SPS-cycle | READ/WRITE | 3072            |

|                   |                                               |            |                 |

| 1F00 <sub>H</sub> | Component identification                      |            | 16              |

|                   |                                               |            |                 |

| 1FE0 <sub>H</sub> | Semaphores                                    |            | 16              |

| 1FFA <sub>H</sub> | Interrupt selection                           | WRITE      | 2               |

| 1FFC <sub>H</sub> | If and which (ISA) Interrupt (PC104)          | WRITE      | 2               |

| 1FFE <sub>H</sub> | Interrupt (ISA)                               | WRITE      | 2               |

| '' ' <b>└</b> Ħ   | interrupt (10/1)                              | VVI XIII L |                 |

# 5.5 Communication (DPRAM offset 1000H)

| DPRAM<br>OFFSET   | FUNCTION                                        |  |  |

|-------------------|-------------------------------------------------|--|--|

|                   |                                                 |  |  |

|                   |                                                 |  |  |

| 1010 <sub>H</sub> | Request word coupling flag inputs               |  |  |

| 1012 <sub>H</sub> | Acknowlegement word coupling flag inputs        |  |  |

| 1014 <sub>H</sub> | Request word coupling flag outputs              |  |  |

| 1016 <sub>H</sub> | Acknowlegement word coupling flag outputs       |  |  |

|                   |                                                 |  |  |

| 1020 <sub>H</sub> | Number of the data block for reading data block |  |  |

| 1022 <sub>H</sub> | Offset in the data block for reading data block |  |  |

| 1024 <sub>H</sub> | Number of words to be read from the data block  |  |  |

| 1026 <sub>H</sub> | Request word Read data block                    |  |  |

| 1028 <sub>H</sub> | Acknowledgement word Read data block            |  |  |

| 102A <sub>H</sub> | Number of the data block for writing data block |  |  |

| 102C <sub>H</sub> | Offset in the data block for writing data block |  |  |

| 102E <sub>H</sub> | Number of words to be written in the data block |  |  |

| 1030н             | Request word Write data block                   |  |  |

| 1032 <sub>H</sub> | Acknowledgement word Write data block           |  |  |

| 1034 <sub>H</sub> | SPC coupling: Output data ready PLC             |  |  |

| 1036 <sub>H</sub> | SPC coupling: Reading output data PC            |  |  |

| 1038 <sub>H</sub> | SPC coupling: Read input data PC                |  |  |

| 103A <sub>H</sub> | SPC coupling: Input data read PLC               |  |  |

| 103С <sub>н</sub> |                                                 |  |  |

| 103E <sub>H</sub> |                                                 |  |  |

| 1040 <sub>H</sub> | Status PLC                                      |  |  |

| 1042 <sub>H</sub> | USTACK error                                    |  |  |

| 1044 <sub>H</sub> | PLC special functions                           |  |  |

| 1046 <sub>H</sub> | Reset error PLC                                 |  |  |

| 1048 <sub>H</sub> | FB error                                        |  |  |

| 104A <sub>H</sub> | Status Register SPC Hardware                    |  |  |

| 104C <sub>H</sub> | Diagnosis register 1                            |  |  |

| 104E <sub>H</sub> | Diagnosis register 2                            |  |  |

| 1060 <sub>H</sub> | SPS-cycle time in ms                            |  |  |

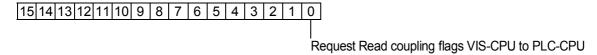

# 5.5.1 Transmission of the coupling flags

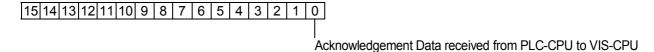

# Description of the data transfer Reading coupling flags (inputs):

Set bit 0 in the request word to 1 in order to start data exchange. When the PLC-CPU has copied the data to the DPRAM, it sets bit 0 in the acknowledgement word. Thereupon the VIS-CPU reads the data from the data range "Coupling flags inputs" (DPRAM offset 500<sub>H</sub>) and resets bit 0 in the request word to 0 in order to indicate to the PLC-CPU that it has read the data. The PLC-CPU on its part then sets bit 0 in the acknowledgement word back to 0.

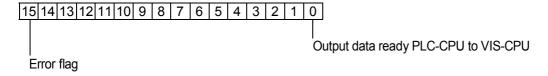

# Request word Coupling flags Inputs DPRAM offset 1010<sub>H</sub>

# Acknowledgement word Coupling flags Inputs DPRAM offset 1012<sub>H</sub>

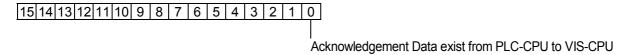

# **Description of the data transfer Writing the coupling marks (outputs):**

First the coupling flags outputs are written in the provided data range (DPRAM offset  $600_H$ ). Then bit 0 is set in the request word. After receiving the data from the PLC-CPU, the latter sets bit 0 in the acknowledgement word. This induces the VIS-CPU to delete bit 0 in the request word, which is then acknowledged by the PLC-CPU by deleting bit 0 in the acknowledgement word.

# Request word Coupling flags Outputs DPRAM offset 1014<sub>H</sub>

### Acknowledgement word Coupling flags Outputs DPRAM offset 1016<sub>H</sub>

TR - Systemtechnik GmbH, Eglishalde 6, 78647 Trossingen, Tel. +49 - (0) 7425-228-0, Fax +49 - (0) 7425-228-34

Date: 27.10.1999

TRS - V - BA - GB - 0094 - 04

Page 24 of 47

### 5.5.2 Transfer of a data block

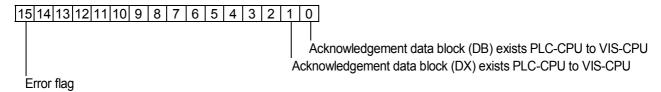

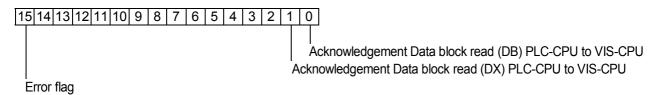

# Description of the data transfer Reading a data block (DB or DX):

First the number of the data block, the offset in the data block and the number of the data words to read are written in the DPRAM. Then the bit is set in the request word in order to start data exchange. When the PLC-CPU has copied the data to the DPRAM, it sets the corresponding bit in the acknowledgement word. Thereupon the VIS-CPU reads the data and resets the bit in the request word in order to indicate to the PLC-CPU that it has read the data. The PLC-CPU on its part then resets the bit in the acknowledgement word to 0. If an error has occurred while reading a data block, the error flag is set in the acknowledgement bit. The actual error code can then be read in the error word.

# Request word Read data block DPRAM offset 1026<sub>H</sub>

# Acknowledgement word Read data block DPRAM offset 1028<sub>H</sub>

### Description of the data transfer Writing a data block (DB or DX):

First the number of the data block, the offset and the number of the data words to write are written in the DPRAM. Then the bit is set in the request word in order to start data exchange. When the PLC-CPU has read the data from DPRAM, it sets the bit in the acknowledgement word. Thereupon the VIS-CPU resets the bit in the request word, which is then acknowledged by the PLC-CPU by deleting the bit in the acknowledgement word.

#### Request word Write data block DPRAM offset 1030<sub>H</sub>

# Acknowledgement word Write data block DPRAM offset 1032<sub>H</sub>

TR - Systemtechnik GmbH, Eglishalde 6, 78647 Trossingen, Tel. +49 - (0) 7425-228-0, Fax +49 - (0) 7425-228-34

Date: 27.10.1999

TRS - V - BA - GB - 0094 - 04

Page 25 of 47

# 5.5.3 Coupling of several SPC components

If a system contains several SPC components, it offers the facility that these components can interchange data, if required. For this, the DPRAM contains 8 blocks with 32 words each. One block for output data where the SPC component stores data for other SPCs (transmitting data) and 7 blocks for input data for receiving data from other SPC components.

| Output data (32 words)  |

|-------------------------|

| Input data 1 (32 words) |

| Input data 2 (32 words) |

| Input data 3 (32 words) |

| Input data 4 (32 words) |

| Input data 5 (32 words) |

| Input data 6 (32 words) |

| Input data 7 (32 words) |

The data to be sent and received are stored in a data block. This data block can be selected in the data block DB 1 itself and must be filled completely before use (e.g. with 0 in all data words). Furthermore, data block DB 1 serves for selecting how many SPCs take part in the data exchange and how many data words are exchanged. Data transfer to the individual SPCs is performed by the higher-level visualization CPU.

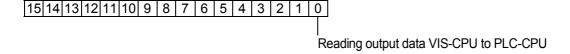

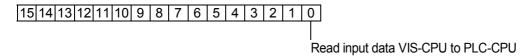

# **Description Read output data:**

The VIS-CPU checks whether the output data are available in the PLC-CPU (Bit 0 = 1 in the word Output data ready). If they are ready, the VIS-CPU can inhibit rewriting of the data by the PLC-CPU by setting bit 0 in the word Reading output data, until it has read all the data. This is necessary to ensure data consistency.

### Communication word Output data ready DPRAM offset 1034<sub>H</sub>

#### Communication word Reading output data DPRAM offset 1036<sub>H</sub>

TR - Systemtechnik GmbH, Eglishalde 6, 78647 Trossingen, Tel. +49 - (0) 7425-228-0, Fax +49 - (0) 7425-228-34

Date: 27.10.1999

TRS - V - BA - GB - 0094 - 04

Page 26 of 47

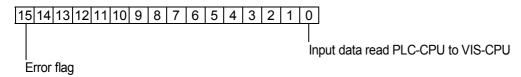

### **Description Read input data:**

The VIS-CPU writes the input data in the DPRAM and sets bit 0 in the communication word Read input data. The PLC-CPU writes the data in the provided data block and acknowledges the receipt of data by setting bit 0 in the communication word Input data read. Thereupon the VIS-CPU recalls its bit, which is acknowledged by the PLC-CPU by recalling its bit.

# Communication word Read input data DPRAM offset 1038<sub>H</sub>

# Communication word Input data read DPRAM offset 103A<sub>H</sub>

# 5.5.4 Status and error messages

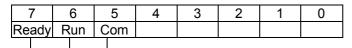

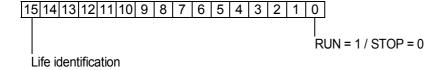

## Status word of the PLC at DPRAM offset 1040<sub>H</sub>

The status word indicates whether the PLC is in state RUN or STOP. Moreover, a bit Life identification is defined. The bit for life identification is set by the PLC-CPU in every cycle. To check whether the PLC is still running, the VIS-CPU sets the bit to 0, then checks if it changes back to 1.

#### Error word for USTACK errors of the PLC at DPRAM offset 1042<sub>H</sub>

All error messages displayed in the USTACK are also output to the dual-ported RAM. For the corresponding error messages, see table USTACK error messages. Low byte = Error code

High byte = Extended error code

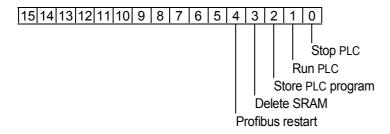

#### Special functions of the PLC at DPRAM offset 1044<sub>H</sub>

The functions "Stop PLC" and "Run PLC" correspond to the RUN/STOP switch (switch 2) mounted on the hardware. They allow to switch the PLC to Stop and back to the Run state via the DPRAM. The function "Store PLC configuration" corresponds to the function of the switch Store configuration (switch 1) mounted on the hardware.

The function "Delete SRAM" deletes the SRAM if it is available on the SPC.

The function "Profibus restart" restarts the profibus if the profibus communication has been aborted by an error. This function is necessary since the PLC does not switch to the STOP state if an profibus error occurs. The same function can be executed via the status FB.

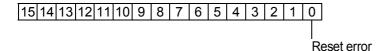

# Reset error message at DPRAM offset 1046<sub>H</sub>

Resetting the error message by setting bit 0. The PLC deletes this bit after deleting the error message.

#### Error word for FB error of the PLC at DPRAM offset 1048<sub>H</sub>

All error messages output to the status module in the parameters ENR und ERC are also output to dual-ported RAM. For the corresponding error messages, see table Functional module error messages.

Low byte = ENR High byte = ERC

Status register SPC hardware on DPRAM offset  $104A_H$  Diagnosis register 1 on DPRAM offset  $104C_H$  Diagnosis register 2 on DPRAM offset  $104E_H$

The values of these 3 registers have the same contents as in status FB.

# 5.5.5 Component identification

The component identification is set in the DPRAM as from the address  $1F00_H$  and is defined in blocks with max. 16 byte each as follows:

| 1. Block: | SPC-LWL R4.02 | (hardware identification and software version number) |

|-----------|---------------|-------------------------------------------------------|

| 2. Block: | 18.01.1999    | (creation date of the current software version)       |

| 3. Block: | PLC-Ver 1.59  | (software version number of the PLC software)         |

# 5.5.6 Transfer of 5 data blocks in a SPS-cycle

In order to achieve a faster transfer, a function has been installed which allows to transfer 5 data blocks in a SPS-cycle. For this, a simplified handshake has been defined. On the normal transfer of data blocks, at least 2 SPS-cycles were needed to transfer a data block.

However, this function has a restriction. In one cycle only 5 data blocks can be read or written, as the data range for the data blocks has to be used for Reading and Writing due to the size of the DPRAM.

# **Division of the DPRAM memory:**

| DPRAM             | FUNKTION                                                                          |  |  |  |

|-------------------|-----------------------------------------------------------------------------------|--|--|--|

| OFFSET            |                                                                                   |  |  |  |

| 1300 <sub>H</sub> | Request word Read data block                                                      |  |  |  |

| 1302 <sub>H</sub> | Reserve                                                                           |  |  |  |

| 1304 <sub>H</sub> | Request word Write data block                                                     |  |  |  |

| 1306 <sub>H</sub> | Reserve                                                                           |  |  |  |

| 1308 <sub>H</sub> | Number first data block. Number = FFFF <sub>H</sub> this data block is not used.  |  |  |  |

| 130A <sub>H</sub> | Offset in the first data block                                                    |  |  |  |

| 130C <sub>H</sub> | Number of words to be read or written from the first data block.                  |  |  |  |

| 130E <sub>H</sub> | Number second data block. Number = FFFF <sub>H</sub> this data block is not used. |  |  |  |

| 1310 <sub>H</sub> | Offset in the second data block                                                   |  |  |  |

| 1312 <sub>H</sub> | Number of words to be read or written from the second data block.                 |  |  |  |

| 1314 <sub>H</sub> | Number third data block. Number = FFFF <sub>H</sub> this data block is not used.  |  |  |  |

| 1316н             | Offset in the third data block                                                    |  |  |  |

| 1318 <sub>H</sub> | Number of words to be read or written from the third data block.                  |  |  |  |

| 131A <sub>H</sub> | Number fourth data block. Number = FFFF <sub>H</sub> this data block is not used. |  |  |  |

| 131C <sub>H</sub> | Offset in the fourth data block                                                   |  |  |  |

| 131E <sub>H</sub> | Number of words to be read or written from the fourth data block.                 |  |  |  |

| 1320 <sub>H</sub> | Number fifth data block. Number = FFFF <sub>H</sub> this data block is not used.  |  |  |  |

| 1322 <sub>H</sub> | Offset in the fifth data block                                                    |  |  |  |

| 1324 <sub>H</sub> | Number of words to be read or written from the fifth data block.                  |  |  |  |

| 1500 <sub>H</sub> | Data range first data block (512 byte)                                            |  |  |  |

| 1700 <sub>H</sub> | Data range second data block (512 byte)                                           |  |  |  |

| 1900н             | Data range third data block (512 byte)                                            |  |  |  |

| 1B00 <sub>H</sub> | Data range fourth data block (512 byte)                                           |  |  |  |

| 1D00 <sub>H</sub> | Data range fifth data block (512 byte)                                            |  |  |  |

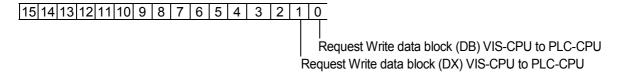

# Description of the data transfer Reading 5 data blocks:

First the number of the data block, the offset and the number of the data words to read for the 5 data blocks are written into the corresponding addresses of the DPRAM. Then the bit is set in the request word in order to start data exchange. When the PLC-CPU has copied the data to the data ranges of the various data blocks in the DPRAM, it resets the bit in the request word. If an error has occurred while reading a data block, the error flag is set in the acknowledgement bit. The actual error code can then be read in the error word. If less than 5 data blocks are to be transferred, FFFF<sub>H</sub> has to be entered into the number of the unused data block

### Request word Read data blocks DPRAM-Offset 1300<sub>H</sub>

Request Read 5 data blocks VIS-CPU to PLC-CPU

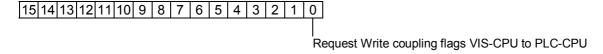

# **Description of the data transfer Writing 5 data blocks:**

First the number of the data block, the offset, the number of the data words to write and the data for the 5 data blocks are written into the corresponding addresses of the DPRAM. Then the bit is set in the request word in order to start data exchange. When the PLC-CPU has read the data from DPRAM, it resets the bit in the request word. If an error has occurred while writing a data block, the error flag is set in the acknowledgement bit. The actual error code can then be read in the error word. If less than 5 data blocks are to be transferred, FFFF<sub>H</sub> has to be entered into the number of the unused data block

#### Request word Write data block DPRAM-Offset 1034<sub>H</sub>

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Request Write 5 data blocks VIS-CPU to PLC-CPU

# 6 Configuration of the realtime PLC

The data for configuring the realtime PLC are stored in the file "PBSDRV.INI" and loaded on starting the program. This file contains an ASCII file and can be edited by means of any editor. However, the indicators in square brackets and the other indicators must not be modified. Modifications may only be performed on the right of the "=" sign.

To modify the file "PBSDRV.INI", the SPC must be booted in interlink mode.

The file PBSDRV.INI contains as follows:

[UPDATE] KOPSPC=0 TEILFAKT=10

[SPS] STATUSFB=10

[HW] NPS=2 SAVEDEST=3

KOPSPC: Determines whether a coupling of several SPCs is required or not. If KOPSPC =

1, the coupling interface is processed, otherwise it is not processed.

TEILFAKT: Determines the period in ms in which the cyclic monitoring function is interrupted

during an OB1 cycle.

STATUSFB: Determines the functional module which is used for the STATUS FB. This module

is available in the SourceCode of the profibus driver and should not be

overwritten by the PLC.

NPS: NPS = 0 no NPS.

NPS = 1 NPS with power supply unit and accumulator NPS = 2 NPS with TRS NPS power supply unit and SRAM

SAVEDEST: SAVEDEST = 0 PLC program is stored in a flash Eprom during storage

SAVEDEST = 1 PLC program is stored in a flash Eprom during storage SAVEDEST = 2 PLC program is stored in an SRAM during storage

SAVEDEST=3 PLC program is stored in a flash Eprom and in an SRAM during

storage

# 7 Types of the SPC and their function

### 7.1 SPC without NPS

In the file "PBSDRV.INI" for this type, the parameter NPS must be 0 and the parameter SAVEDEST must be 0 or 1. If storage for this type was performed in the SRAM, the data would get lost after switching off.

If the SPC is switched on and the realtime PLC is started, the latter checks whether the FLASH-DISK contains a valid PLC program. If so, it loads the program and checks the checksum. If the checksum is OK and the field bus operates properly, the PLC switches to the RUN state.

If the checksum is not OK, an error message is output to the display of the SPC and to the USTACK. The PLC then must be restarted by initial deletion from the programmer and by repeated transmission of the PLC program to the SPC. The RUN/STOP and STORE keys at the SPC are disabled until initial deletion has been executed.

If there is no NPS, the state of the PLC program, which has also been active during the last manual storage, is active again after switching the SPC off and on. This signifies no remanent flags and data block contents.

# 7.2 SPC with NPS power supply unit and accumulator

In the file "PBSDRV.INI" for this type, the parameter NPS must be 1 and the parameter SAVEDEST must be 0 or 1. If storage for this type was performed in the SRAM, the data would get lost after switching off.

If the SPC is switched on and the realtime PLC is started, the latter checks whether the FLASH-DISK contains a valid PLC program. If so, it loads the program and checks the checksum. If the checksum is OK and the field bus operates properly, the PLC switches to the RUN state.

If the checksum is not OK, an error message is output to the display of the SPC and to the USTACK. The PLC then must be restarted by initial deletion from the programmer and by repeated transmission of the PLC program to the SPC. The RUN/STOP and STORE keys at the SPC are disabled until initial deletion has been executed.

If the PLC program runs and voltage loss is detected, the PLC program is stored in the FLASH disk. This is indicated by the flashing error message "FF" in the status display on the SPC. Storage takes approx. 6 sec. For this type, however, please note that the PLC program is not stored on switching off the computer regularly via the mains switch of the computer power supply unit.

For this NPS type, the state of the PLC program, which has also been active during the last manual storage, is also active again after switching the SPC off and on. This signifies no remanent flags and data block contents. If flags and data block contents shall be remanent, the computer must not be switched off via the switch of the computer power supply unit.

# 7.3 SPC with TRS NPS power supply unit

In the file "PBSDRV.INI" for this type, the parameter NPS must be 2 and the parameter SAVEDEST must be 2 or 3.

If the SPC is switched on and the realtime PLC is started, the latter checks whether the SRAM contains a valid PLC program. If so, it loads the program and checks the checksum. If the checksum is OK and the field bus operates properly, the PLC switches to the RUN state.

If the checksum is not OK, an error message is output to the display of the SPC and to the USTACK. The PLC then must be restarted by initial deletion from the programmer and by repeated transmission of the PLC program to the SPC. The RUN/STOP and STORE keys at the SPC are disabled until initial deletion has been executed.

If there is no program in the SRAM, an error message is also output to the display of the SPC and to the USTACK. However, it is now possible to reload the program from the FLASH disk. Of course, the prerequisite for this is that the parameter SAVEDEST is set to 3. If not, there is no PLC program on the FLASH disk.

To reload from the FLASH disk, press the Reload Flash key and actuate the memory switch from left to right and back 3 times within 6 seconds. The Reload Flash key must be actuated during the whole reload procedure.

If a reading error or a checksum error is detected on loading from the FLASH disk, an error message is output; then proceed in the same manner as for an SRAM checksum error.

If no program is found in the SRAM nor on the FLASH disk, it must be transmitted from the programmer again.

If the PLC program runs and voltage loss is detected, the PLC program is stored in the SRAM. This is indicated by the flashing error message "FF" in the status display on the SPC. Storage takes approx. 300 msec. For this type, storage is also performed on normally switching off the computer by the mains switch of the computer power supply unit. Flags and data block contents are remanent for this type, provided that the flags to be kept remanent are configured in the DB 1.

The TRS NPS power supply unit requires a charging time of 1.5 minutes to ensure sufficient load for buffering. If a voltage loss or switching off occurs within these 1.5 minutes after switching on the SPC, no storage is performed.

# 7.4 Manual storage

There are 3 ways to store the PLC program on the FLASH disk or in the SRAM manually.

- 1. Storage via the memory switch at the SPC.

- 2. Storage via the dual-ported RAM by setting the corresponding bit in the word "Special functions of the PLC" at DPRAM offset 1044<sub>H</sub>.

- 3. Storage via the programmer. For storage via the programmer, the PLC must be set in the STOP state, then compression must be started. The PLC program is then compressed and stored afterwards.

# 8 Hardware description SPC base board

(Dual-ported RAM module for installation of a slave PC in an ISA system)

# 8.1 General information

The SPC-XXX is a PC plug-in board. It serves mainly for separating a PC-104 CPU and a PC-104 field bus interface from the ISA bus by means of a dual-ported RAM. Furthermore, it provides various periphery functions for the PC-104 bus, which are described in the following chapters.

### 8.2 Functions of the board

#### The board contains the following functions:

- 2 pcs. PC-104 interfaces for plugging the local CPU and other PC-104 components.

- Dual-ported RAM coupling between ISA bus and local CPU optionally with 4K\*16bit or 8K\*16bit dual-ported RAM. The dual-ported RAM begins at the address D000:0000. From the outside (ISA BUS), the address range can be adjusted via a hex switch at the top of the board. The interrupt and semaphore logic of the dual-ported RAM is decoded.

- Register for determining the dual-ported RAM interrupt on the ISA bus

- 1 MB buffered SRAM, divided into 32 pages with 32 KB each

- OWG master interface

- CAN master interface

- COM1 and COM2 of the plugged PC-104 CPU are lead through sub-D plugs.

- NPS power supply unit logic

- Battery connection for external battery via NPS port

- Voltage monitoring of the NPS battery

- Voltage monitoring of the external battery

- Switch for Run/Stop and update function

- Reset key for local reset

- 2 pcs. 7-segment display for indicating diagnosis, operation and error messages

- Timer for triggering an NMI on the local CPU and, if required, also on the ISA bus

#### 8.3 Addresses on the ISA bus

As standard, a DP-RAM of 8KB organized with 4K\*16bit is mounted on the module. The address range of the ISA page can be displaced in 8 steps of 8K by means of the hex switch S200 on top of the module. The upper addresses of the DP-RAM dispose of special functions (see table below).

| Switch   | Normal        | Set INT (Wr)  | Clr INT (Rd)    | ISA interrupt select |

|----------|---------------|---------------|-----------------|----------------------|

| position | address range | to PC-104 CPU | from PC-104-CPU |                      |

|          |               |               |                 |                      |

| 0        | D0000HD1FDFH  | D1FFCH        | D1FFEH          | D1FFAH               |

| 1        | D2000HD3FDFH  | D3FFCH        | D3FFEH          | D3FFAH               |

| 2        | D4000HD5FDFH  | D5FFCH        | D5FFEH          | D5FFAH               |

| 3        | D6000HD7FDFH  | D7FFCH        | D7FFEH          | D7FFAH               |

| 4        | D8000HD9FDFH  | D9FFCH        | D9FFEH          | D9FFAH               |

| 5        | DA000HDBFDFH  | DBFFCH        | DBFFEH          | DBFFAH               |

| 6        | DC000HDDFDFH  | DDFFCH        | DDFFEH          | DDFFAH               |

| 7        | DE000HDFFDFH  | DFFFCH        | DFFFEH          | DFFFAH               |

# 8.3.1 Terms

#### Normal address range

This range is the normal DP-RAM.

#### INT

If this address (word) is described by the ISA bus, an interrupt is triggered on the PC-104 CPU. The prerequisite is that an interrupt is activated by bridge and the corresponding interrupt is released (see bridge assignment). The interrupt is deleted by the PC-104 page by reading the same cell. Furthermore, the address disposes of a normal DP-RAM function.

#### **CIr INT**

By reading this address, an interrupt generated by the PC-104 bus is reset. The interrupt must be activated by describing the ISA interrupt select address and released in the interrupt controller, so that it becomes active on the ISA bus (see below). Furthermore, the address disposes of a normal DP-RAM function.

# ISA interrupt select

It is possible to select by writing a data word in this address if and which interrupt from the DP-RAM is generated on the ISA bus. After a reset, the interrupt is disabled.

| Data word | Interrupt |

|-----------|-----------|

| 0         | IRQ 5     |

| 1         | IRQ 7     |

| 2         | IRQ 9     |

| 3         | IRQ 10    |

| 4         | IRQ 11    |

| 5         | IRQ 12    |

| 6         | IRQ 15    |

| 7         | disabled  |

### 8.4 Functions on the local PC-104 bus

# 8.4.1 Memory addresses on the local PC-104 bus

As standard, the memory address ranges on the local bus cannot be displaced. However, they can be modified by reprogramming a PAL. Optionally, displacement by bridges is also possible.

#### 8.4.1.1 DP-RAM

The upper addresses of the DP-RAM dispose of special functions (see table below).

| Normal        | Set INT (Wr)<br>to ISA-CPU | CIr INT (Rd)<br>from ISA-CPU |

|---------------|----------------------------|------------------------------|

| address range | IU ISA-CPU                 | HOITISA-CPU                  |

| D0000HD1FDFH  | D1FFEH                     | D1FFCH                       |