# User's Manual

I/O Logic Controller

Price: \$25.00

# Important User Information

Because of the variety of uses for the solid state equipment described herein, and because of the differences between it and electromechanical equipment, you must satisfy yourself as to its acceptability for each of your applications. In no event will Allen-Bradley Company be responsible or liable for indirect or consequential damages that may result from installation or use of this equipment.

The illustrations, charts, and layout examples shown in this manual are intended solely to help you understand the text, not to guarantee operation. Because of the many variables and requirements associated with any particular installation, Allen-Bradley Company will not assume responsibility for actual use based upon illustrations of applications.

No patent liability is assumed by Allen-Bradley Company with respect to use of information, circuits, equipment, or software described in this text.

Reproduction of any part of this manual, without written permission of Allen-Bradley Company, is prohibited.

© 1986 Allen-Bradley Company

PLC is a registered trademark of Allen-Bradley Company

| Chapter | Title Page                                                                                                                                                                                                                                                                |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Using this manualChapter objectives1-1What this manual contains1-1Audience1-1Definitions of major terms1-2Warnings and cautions1-2Related publications1-2Chapter summary1-2                                                                                               |

| 2       | Introducing the I/O Logic ControllerChapter objectives2-1Example applications2-1Module functions2-1Compatible processors2-2Compatible I/O devices2-3Module description2-3Status indicators2-3Output fuses2-4Terminal identification2-4Specifications2-5Chapter summary2-5 |

| 3       | Installing your moduleChapter objectives3-1Keying3-1Power requirements3-1Input power supply3-2Output power supply3-2Wiring-arm connections3-3Installing your module3-3Response to an external fault3-4Electrostatic discharge3-4Chapter summary3-4                        |

| Chapter | Title                                           | Page |

|---------|-------------------------------------------------|------|

| 4       | Module/Processor Communication                  |      |

|         | Chapter objectives                              | 4-1  |

|         | Block-transfer                                  |      |

|         | Block-transfer-write data                       |      |

|         | Rung format                                     |      |

|         | Input and output instructions                   |      |

|         | Output select                                   |      |

|         | Preset value                                    |      |

|         | Accumulated value                               |      |

|         | Time                                            |      |

|         | Program formats for various output instructions | _    |

|         | Input branch conditions                         |      |

|         | Response time                                   |      |

|         | Up counter instruction                          |      |

|         | Counter reset instruction                       |      |

|         | Down counter instruction                        |      |

|         | Timer instruction                               |      |

|         | Timed event counter instruction                 |      |

|         | Timer reset instruction                         |      |

|         | Block-transfer-read data                        |      |

|         | Word 1 - Status flags                           |      |

|         | Word 2 - Hardware outputs and inputs            |      |

|         | Word 3 - Logical outputs and composite inputs   |      |

|         | Word 4 - Binary value specified with            |      |

|         | SETID command                                   | 4-18 |

|         | Words 5,6,7 and 8 - Binary coded decimal        |      |

|         | (BCD) counts                                    | 4-18 |

|         | Word 9 - Error code and error word pointer      | 4-18 |

|         | Word 10 - Control processor series/revision and |      |

|         | communication processor series/revision         | 4-19 |

|         | Programming example                             | 4-20 |

|         | Programming errors                              | 4-21 |

|         | Programming boundaries                          |      |

|         | Commands                                        | 4-22 |

|         | Configuration data commands                     | 4-23 |

|         | On-line commands                                | 4-27 |

|         | Mask input programming examples for PLC-2 and   |      |

|         | PLC-3 family processors                         |      |

|         | PLC-2 family processors                         | 4-28 |

|         | Rung descriptions for mask input PLC-2 family   |      |

|         | processor example program                       |      |

|         | PLC-3 family processors                         | 4-30 |

|         | Rung descriptions for PLC-3 family processor    |      |

|         | example program                                 | 4-33 |

| Chapter         | Title                                                                                                                                                                                                                  | Page                         |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|                 | SETID programming examples PLC-2 family processors Rung descriptions for the PLC-2 family processor SETID program PLC-3 family processors Rung descriptions for PLC-3 family SETID programming example Chapter summary | 4-33<br>4-36<br>4-37<br>4-40 |

| 5               | Troubleshooting Chapter objectives Troubleshooting table Causes of block-transfer errors Errors indicated by diagnostic bits Chapter summary                                                                           | . 5-1<br>. 5-2<br>. 5-2      |

| Appendices<br>A | Block-transfer timing                                                                                                                                                                                                  | A-1                          |

| В               | Hex input conversion table                                                                                                                                                                                             | B-1                          |

| С               | Block-transfer ladder diagram examples                                                                                                                                                                                 | C-1                          |

### Chapter objectives

Read this chapter to familiarize yourself with this manual. It tells you how to use the manual properly and efficiently.

# What this manual contains

| Chapter    | Title                                     | Topics Covered                                         |  |  |  |  |

|------------|-------------------------------------------|--------------------------------------------------------|--|--|--|--|

| 1          | Using this manual                         | Manual's purpose, audience and contents                |  |  |  |  |

| 2          | Introducing the I/O<br>Logic Controller   | Module description, features and hardware components   |  |  |  |  |

| 3          | Configuring and installing your module    | Keying, power requirements, wiring and installation    |  |  |  |  |

| 4          | Module/Processor communication            | Word and file parameters of block transfer data        |  |  |  |  |

| 5          | Troubleshooting                           | Troubleshooting guide                                  |  |  |  |  |

| Appendices |                                           |                                                        |  |  |  |  |

| A          | Block transfer timing                     | Instructions for determining block-<br>transfer timing |  |  |  |  |

| В          | Hex input conversion table                |                                                        |  |  |  |  |

| С          | Block-transfer ladder<br>diagram examples | Examples of block-transfer programming                 |  |  |  |  |

### **Audience**

We assume that you know how to:

- program and operate an Allen-Bradley programmable controller.

- program block-transfer instructions.

If you don't know how to do either of these, read the user's manual for your processor. Refer to Allen-Bradley Industrial Computer Group Publication Index (publication SD 499) for a complete list of publications.

### Definitions of maior terms

To make this manual easier for you to read and understand, we avoid repeating product names where possible. We refer to:

- programmable controllers, as the "processor".

- the I/O Logic Controller, as the "controller".

For a list of PC words and their definitions, contact your Allen-Bradley sales engineer or distributor for publication PCGI-7.2.

### Warnings and cautions

You will see three types of precautionary statements as you read this manual: Important, CAUTION and WARNING.

- Important tells you about specific areas of concern when operating your equipment.

- CAUTION tells you when equipment may be damaged if procedures are not followed properly.

- WARNING tells you when people may be injured if procedures are not followed properly.

## Related publications

Consult the Allen-Bradley Industrial Computer Group Publication Index (SD 499) if you would like more information about your modules or programmable controllers. This index lists all available publications for Allen-Bradley programmable controller products. Also refer to Programmable Controller Grounding and Wiring Guidelines (publication number 1770-4.1) if necessary.

# Chapter summary

This chapter told you how to use this manual efficiently. The next chapter introduces you to the I/O Logic Controller.

### Chapter objectives

This chapter describes:

- example applications of the controller.

- functions of the controller.

- compatible Allen-Bradley processors and I/O devices.

- status indicators, fuses, terminals and specifications.

### Example applications

Use the I/O Logic Controller Module (Cat. No. 1771-DR) in the following applications:

- high speed presence sensing

- high speed canning, bottling, packaging

- conveyor systems for material sorting

- counting high speed events for a selected time period

### Module functions

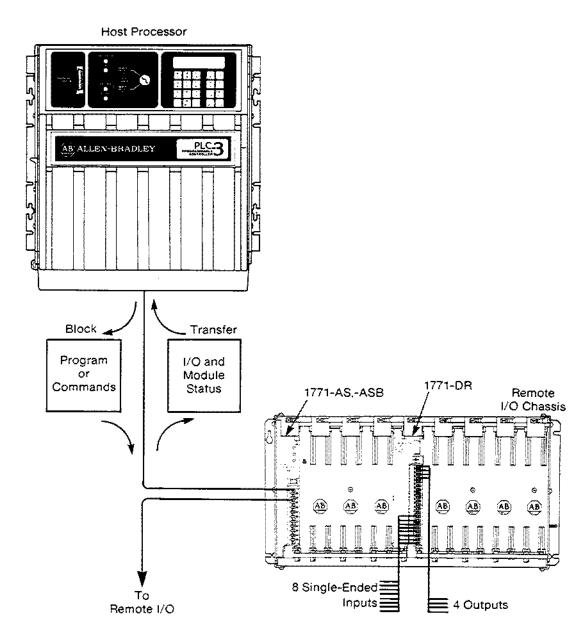

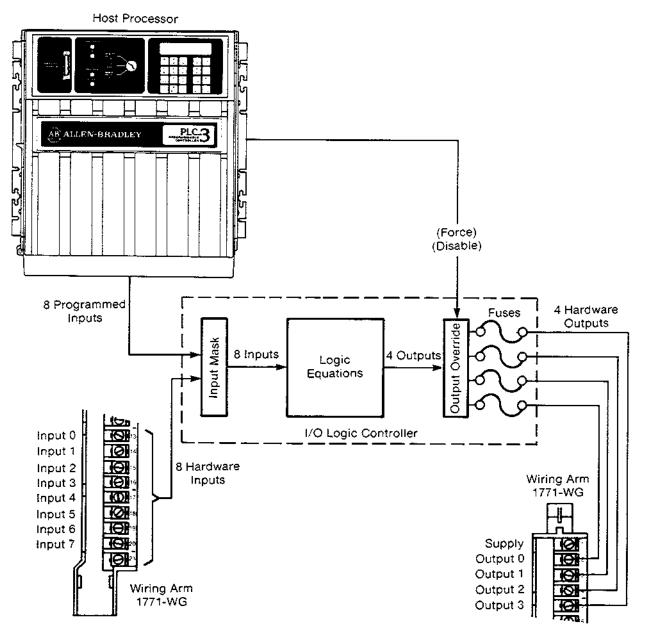

The I/O Logic Controller Module monitors inputs and controls outputs based on the program downloaded from the host processor. It reports I/O status and self-diagnostics back to the host processor (figure 2.1). The controller offers the following functions:

- monitors up to eight discrete inputs.

- accepts input pulses within programmable ranges from 50us to 10ms.

- controls up to four discrete outputs.

- provides response times of less than one millisecond for all four outputs at the same time when the time constant of its input filter is 50 us.

- processes block-transfers to or from the host processor,

- return I/O status, accumulated count values, detected programming errors and self diagnostics to the host processor.

- receive commands, programmed inputs or programs from the host processor.

- masks selected inputs so the host processor can substitute programmed bits in their place.

- forces and/or disables selected outputs upon command.

- accepts on-line changes for synchronization with other events supervised by the host processor.

# Module functions (continued)

Figure 2.1

Block diagram of I/O Logic Controller

14155

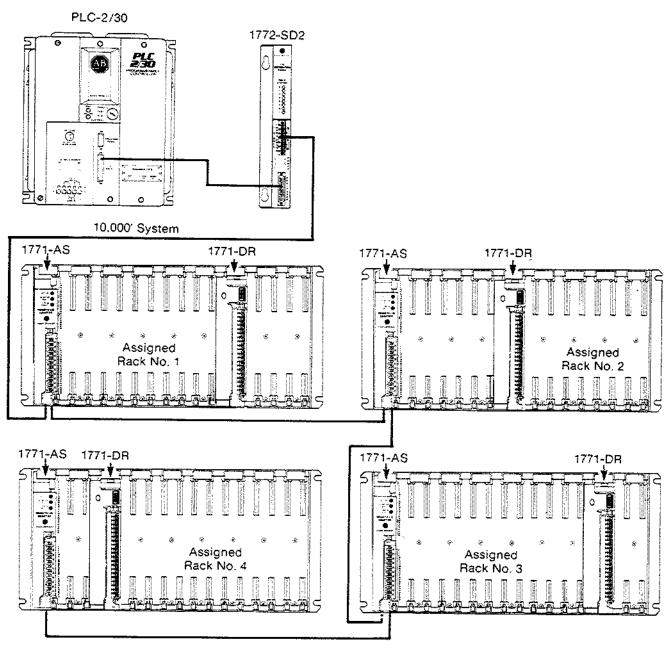

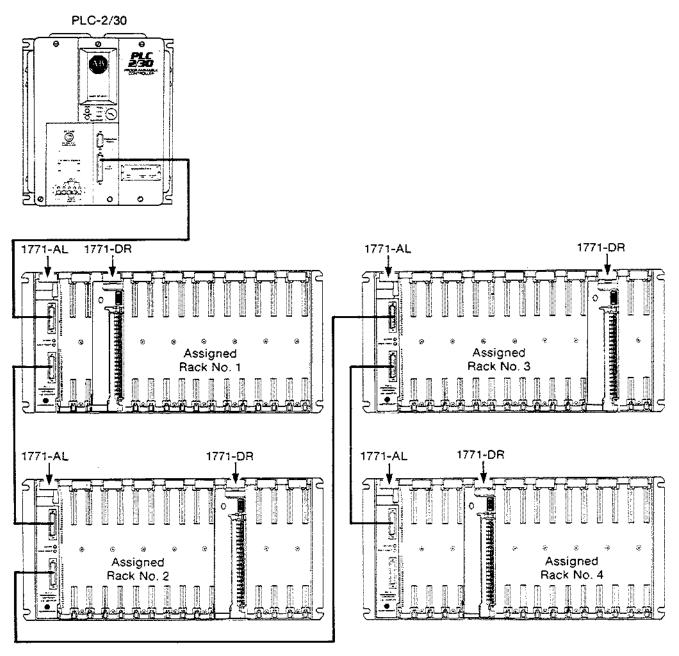

# Compatible processors

You can use the module with any Allen-Bradley processor that uses block transfer programming in both local and remote 1771 I/O systems. Processors that are compatible with the module include:

- Mini-PLC-2 (cat no. 1772-LN3)

- Mini-PLC-2/05 (cat. no. 1772-LS, -LSP)

- Mini-PLC-2/15 (cat. no. 1772-LV)

- Mini-PLC-2/16 (cat. no. 1772-LX,-LXP)

# Compatible processors (continued)

- Mini-PLC-2/17 (cat. no. 1772-LW,-LWP)

- PLC-2/20 (cat. no 1772-LP1, -LP2)

- PLC-2/30 (cat. no. 1772-LP3)

- PLC-3 (cat. no 1775-L1, -L2)

- PLC-3/10 (cat. no. 1775-LP4, -LP8)

# Compatible I/O devices

Typical 12 to 24 V DC 2-wire or 3-wire input switches that you can use with the module include:

- DC proximity switches (A-B Bulletin 871C)

- photoelectric sensors (A-B Bulletin 880L)

- DC limit, float, pushbutton or selector switches (A-B Bulletin 800, 801 and 840)

Typical output devices that the module can control include:

- DC relays (A-B Bulletin 700)

- DC solenoids

- indicators (A-B Bulletin 800)

## Module description

The I/O Logic Controller Module is an intelligent I/O module that offers high speed response independent of the host processor's scan time.

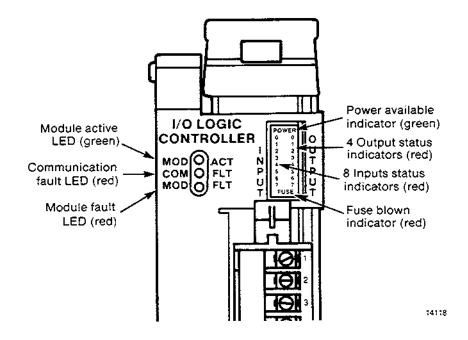

### Status indicators

The module has three LED status indicators on the left LED display (figure 2.2).

- MOD ACT (green) indicates module is up and running.

- COMM FLT (red) indicates a communication fault.

- MOD FLT (red) indicates a hardware fault.

The module also has 14 LED status indicators on the right LED display (figure 2.2).

- 4 red output status indicators (one for each output) light when the corresponding output circuitry is energized.

- 8 red input status indicators (one for each input) light when the corresponding input circuitry is energized.

- Power (green) indicates the modules output circuits are functioning.

- Fuse (red) indicates one or more output fuses have blown.

# Status indicators (continued)

Figure 2.2 LED status indicators

# **Output fuses**

Your module has four 3A rectifier fuses (one per output) located on the right printed circuit board.

# Terminal identification

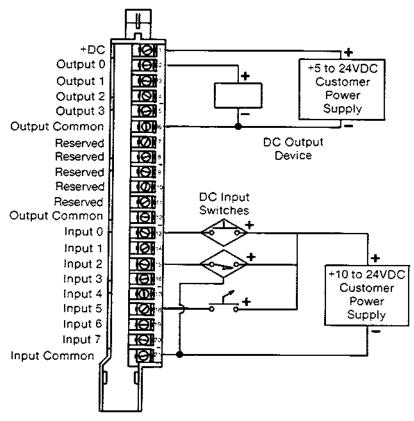

Figure 3.1 shows each terminal on the module.

### Specifications

#### Number and type of inputs

- 8 single-ended

- Current sinking

# Input voltage range and logic state

- Logic 0: 0 to 4.0 V DC

- Logic 1: 10.0 to 24.0 V DC

#### Input current

- 6 mA @ 12 V DC

- 12 mA @ 24 V DC

#### Input isolation

1500 V DC

#### Digital input filtering

- Range: 50 to 9999 us

- Selected by input pairs

#### Input frequency

1 KHz

#### Number and type of outputs

- 4 single-ended

- Current sourcing

# Output voltage range (customer supply)

• 5 to 24 V DC

# Output current rating (per output)

- Continuous: 2 A

- Surge: 4 A for 10 ms

#### **VA** rating

- 48 W per output

- 192 W per module

#### On-state voltage drop

0.25 V DC per output

#### Off-state leakage current

1 mA per output

#### **Output** isolation

1500 V DC

### Output fusing (per output)

3 A recitifier fuse (Littleffuse 322002, Buss GBB003 or equivalent)

### Backplane current

1.1 A @ 5 V DC

#### **Environmental conditions**

- Operating temperature 0° to 60°C (32° to 140°F)

- Storage temperature -40° to 85°C (-40° to 185°F)

- Relative humidity 5% to 95% (without condensation)

#### Module location

Any 1771 I/O chassis I/O group

#### Kevino

- Left connector: between 10 and 12 between 30 and 32

- Right connector: between 10 and 12 between 34 and 36

#### Wiring arm

• (Cat. No. 1771-WG)

# Chapter summary

This chapter described the I/O Logic Controller Module, its functions and applications, and the processors and I/O devices with which it is compatible. The next chapter tells you how to configure and install the module.

|  |  |  | · |  |

|--|--|--|---|--|

|  |  |  |   |  |

|  |  |  |   |  |

# Chapter objectives

This chapter tells you how to:

- key the module

- power controller input circuitry and output devices

- make wiring arm connections

- install the module.

### Keying

Plastic keying bands are shipped with each I/O chassis. These bands ensure that only a selected type of module can be placed in a particular I/O chassis module slot. They also help to align the module with the backplane connector.

Each module is slotted at its rear edge. The position of the keying bands must correspond to these slots to allow insertion of the module. Place the keying bands on the upper backplane connectors between the numbers at the right of the connectors.

- Left connector between 10 and 12 between 30 and 32

- Right connector between 10 and 12 between 34 and 36

## Power requirements

Normally you must provide a minimum of two external power supplies: one to power input circuitry and one to power output devices. You can, however, use one supply if common voltage for both inputs and outputs is acceptable and isolation between inputs and outputs is not necessary.

### Input power supply

Input circuitry does not require the direct hookup of a power supply. Connect the (+) side of the supply to the input device and the (-) side to input common, terminal 21 of the wiring arm (figure 3.1).

Figure 3.1 Connection diagram for input/output devices and power supplies

14157

**Output power supply**

To power the four outputs (figure 3.1) connect a 5 to 24 V DC supply to terminal 1 and terminal 6 of the wiring arm.

# Wiring-arm connections

Refer to figure 3.1 for connection diagrams for input and output devices. There are two output commons associated with outputs 0 through 3 (terminals 6 and 12). One 21 point swing arm (cat. no. 1771-WG) provides all the connection terminals.

# Installing your module

Now that you've determined the power requirements, keying, and wiring for your module, you can use the following procedure to install it.

Refer to Programmable Controller Grounding and Wiring Guidelines (pub. no. 1770-4.1) for proper grounding and wiring methods to install your module.

WARNING: Remove power from the 1771 I/O chassis backplane and wiring arm before removing or installing an I/O module.

- Failure to remove power from the backplane or wiring arm could cause module damage, degradation of performance or injury.

- Failure to remove power from the backplane could cause injury or equipment damage due to possible unexpected operation.

WARNING: Install the module in the I/O chassis so that both halves of the module are in the same I/O group when you select 2-slot addressing. Failure to observe this rule will result in faulty module operation and/or damage to the module circuitry with possible injury to personnel.

When installing your module in an I/O chassis:

- 1. Turn off power to the I/O chassis.

- 2. Open the module locking latch on the I/O chassis and insert the module into the slot keyed for it.

- 3. Firmly press to seat the module into its backplane connector.

# Installing your module

**CAUTION:** Do not force the module into the backplane connector. You can damage the connector and/or the module. If you can't seat the module with firm pressure, check alignment and keying.

- 4. Snap the chassis latch over the top of the module to secure its positon.

- 5. Connect the wiring arm to the module.

# Response to an external fault

Your module operates independent of the host processor except for downloading programs or commands and reporting status. If a processor fault or I/O communications fault occurs, the module either continues or stops operation depending on how you set the last state switch in the module's I/O chassis.

If you set the last state switch to turn outputs off, the module stops operating and turns its outputs off.

If you set the last state switch to hold outputs in last state, the module continues operating.

## Electrostatic discharge

Electrostatic discharge can damage integrated circuits or semiconductors in your module if you touch backplane connector pins. Avoid electrostatic damage by observing the following precautions:

- Touch a grounded object to discharge yourself before handling the module.

- Do not touch the backplane connector or connector pins.

- When not in use, keep the module in its static-shield bag.

**CAUTION:** Electrostatic discharge can degrade performance or damage the module. Handle as stated above.

## Chapter summary

This chapter described the keying, power requirements, wiring and installation of your module. In the next chapter you will read about module/processor communication.

### Chapter objectives

This chapter describes the format of block-transfer-read and write data and includes information on programming your module.

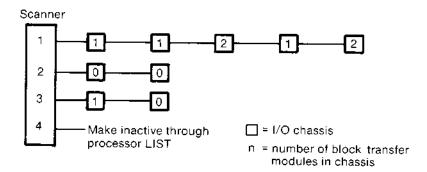

### Block-transfer

The controller module and the host processor communicate through block-transfer programming. Processors that use block-transfer programming are listed below, along with the associated user manual. Refer to the latest edition of the manual for a detailed description of block-transfer.

| Processor     | Publication Number |

|---------------|--------------------|

| Mini-PLC-2    | 1772-6.8.4         |

| Mini-PLC-2/05 | 1772-6.8.6         |

| Mini-PLC-2/15 | 1772-6.8.2         |

| Mini-PLC-2/16 | 1772-6.5.7         |

| Mini-PLC-2/17 | 1772-6.5.6         |

| PLC-2/20      | 1772-6.8.1         |

| PLC-2/30      | 1772-6.8.3         |

| PLC-3, -3/10  | 1775-6.4.1         |

# Block-transfer-write data

You write data from the processor to the module in blocks. You can send a maximum of 64 words in one block-transfer operation. The number of words you send to the module determines how many outputs it controls and the number of input branches to define those outputs. A hex code file resides in the host processor's data table and represents the logic program of the controller. You start the hex code file with an Initialization Command (0001). The initialize command:

- prepares the internal flags for programming.

- clears the memory of the controller.

- stops any I/O processing.

- de-energizes the outputs.

# Block-transfer-write data

(continued)

You end the hex code file with an Execute Command (0003). The Execute Command follows the configuration data and causes the module to begin execution of the most recent program downloaded if no program errors are detected. Between the Initialize Command and Execute Command is the file for the controller's configuration and logic program.

You download this program to the controller using a blocktransfer-write command.

## Rung format

You must translate equivalent rungs of ladder logic to hex files for your logic controller using the following format:

- 1. Output instruction

- 2. Output select

- 3. Preset count for counters (if applicable)/time base for timers (if applicable)

- 4. Accumulated count for counters (if applicable)

- 5. Input branch

- **6.** Input branch (if applicable)

- 7. Input branch (if applicable)

### Input and Output instructions

The controller's instruction set includes the following input and output instructions.

#### Input instructions

—] [—

True when input switch is closed (10-24 V

Examine on

DC at the wiring arm)

—]/[— Examine off True when input switch is open (0-4 V DC

at the wiring arm)

#### **Output instructions**

**—**( )—

Turns on when at least one input branch

Output energize is true.

-(L)-Output latch Turns on when at least one input branch is true and remains on until reset by an

unlatch instruction having the same

output address.

# Input and Output instructions (continued)

—(U)— Output unlatch Turns off a latch instruction having the same output address when at least one input branch is true. It will remain off until set by a latch instruction. When the input conditions for both the latch/unlatch instructions are true, the unlatch instruction overrides the latch instruction.

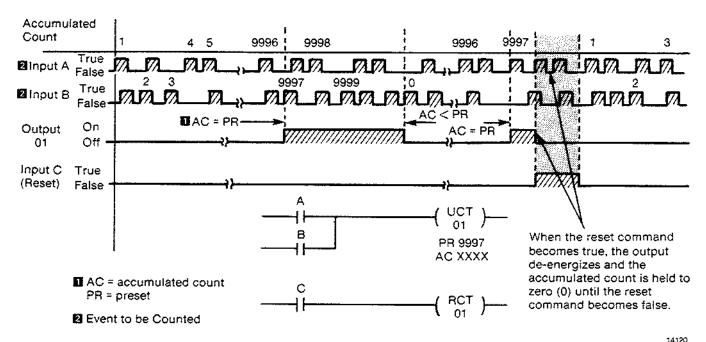

-(UCT)-Up counter

Counts false-to-true rung transitions. A true input branch must go false before the instruction recognizes another false-to-true transition.

You must enter a preset and an initial accumulated value (0 - 9999).

The output energizes when the accumulated value equals or exceeds the preset. The accumulated value will increment to a maximum value of 9999 and then rollover to zero. If the accumulated value rolls to zero and is less then the preset value, the output will deenergize.

The up counter must be reset by the counter reset instruction (RCT) having the same output address.

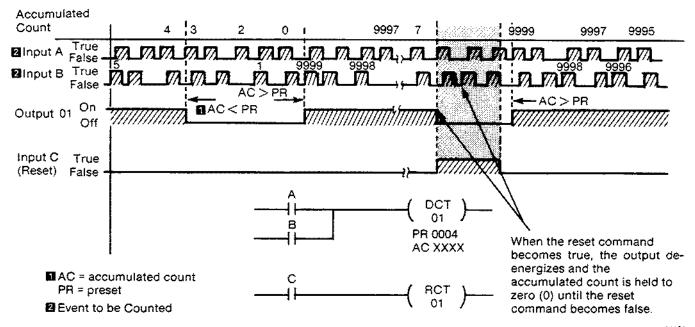

—(DCT)— Down counter Counts down with the same characteristics as an up counter.

—(RCT)— Reset counter

Resets the up or down counter (UCT or DCT) with the same output address. It also de-energizes the output (if the preset value does not equal zero) and resets the accumulated value of the counter to zero when at least one input branch is true.

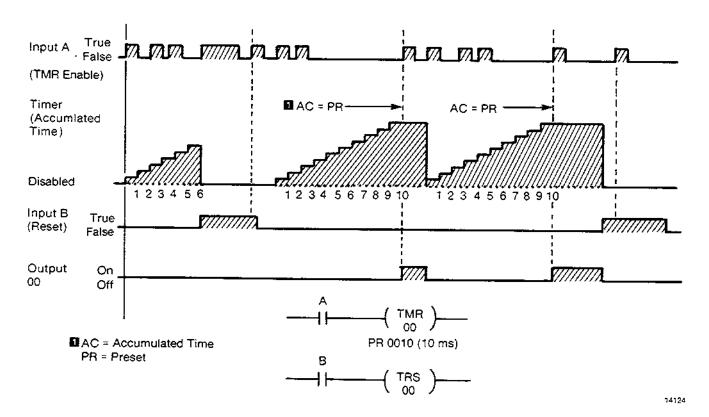

-(TMR)-Timer

Starts timing when at least one input branch changes from false to true. It remains enabled unless it is reset by the Timer Reset Command (TRS) with the same address or until the time has elapsed. The output energizes when the timer "times out".

You must enter a preset between 1 ms and 10 seconds.

### Input and Output instructions (continued)

-(TMR)-(TEC)-Timed Event Counter

The timed event counter is a combination of a counter (TEC) and a timer (TMR). Both instructions have independent branch input conditions, but the same output address. The counter increments when at least one input branch makes a false-to-true transition while the timer is running. The same input branch must become false before another independent branch becomes true to increment the counter.

The output energizes and counting is suspended when the timer "times out".

The accumulated count value (max 9999) is transferred to the host processor in the module's status block (words 5 through 8 depending on which outputs are selected as counters).

The (TEC) instruction latches its accumulated value until reset when the (TMR) instruction is re-enabled.

You must program a preset between 1 ms and 10 seconds for the (TMR) instruction.

The (TMR) instruction is retentive. Once an input branch goes from false-to-true. the timer will continue timing until the preset is reached or the Timer Reset (TRS) with the same address activates.

—(TRS)— Timer reset

Resets the accumulated time value of the (TMR) timer having the same output address and de-energizes the output when at least one input branch of its rung is true.

#### Input and Output instructions (continued)

**WARNING:** Up counter (UCT), down counter (DCT), counter reset (RCT), timer (TMR) and timer reset (TRS) instructions used with the I/O Logic Controller do not operate like the timers and counters associated with Allen-Bradley processors. Refer to figures 4.4, 4.5, 4.6 and the accompanying text for descriptions of operation.

### Output select

You select the output using the form FF XX, where XX = 00through 03. The four outputs are numbered sequentially from 00 to 03.

### Preset value

Use a preset value when you use UCT and/or DCT instructions. The maximum count for a preset is 9999.

#### Accumulated value

A counter accumulated value is generated when you use UCT, DCT or TEC instructions. The accumulated value is programmable from 0000 to 9999 BCD and is returned to the host processor's status block.

- Word 5 BCD count for output 0

- Word 6 BCD count for output 1

- Word 7 BCD count for output 2

- Word 8 BCD count for output 3

### Time

You must enter a time base when you use a TMR instruction. Time base values range from 0.001 seconds (one millisecond) to 10.00 seconds. Enter 0000 for 10.00 seconds.

### Program formats for various output instructions

The following tables show the hex code formats for the various output instructions:

#### OTE, OTL, OTU, RCT, TEC, TRS

- 1. Output instruction

- 2. Output select

- 3. Input branch

- 4. Input branch (if applicable)

#### UCT, DET

- 1. Output instruction

- 2. Output select

- 3. Preset value

- 4. Accumulated value

- 5. Input branch

- 6. Input branch (if applicable)

#### TMR

- 1. Output instruction

- 2. Output select

- 3. Preset Time

- 4. Input branch

- 5. Input branch (if applicable)

# Input branch conditions

When defining the input branch conditions in the hex file, you must first convert branches containing common terms to independent (parallel) branches (figure 4.1).

Figure 4.1 Converting branches containing common terms to parallel branches

wrong right

A B C A B C

Example 1: |---] [---]/[-+-]/[---|

D E | D E C |

|---] [---] [---] [---]/[-+

Repeat input C in each branch

A B C D A B C D

Example 2: |--|/{-+-| [-+-| [-+-| [--| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---| |---

Rewrite into four independent (parallel) branches

### Input branch conditions (continued)

Each word in the hex code file for an independent input branch is divided into an upper and lower byte.

The upper byte represents the number of unique inputs in an independent (parallel) branch. You can program up to eight (8) inputs per branch. The lower byte represents the inputs in a branch which are low true logic (examine off).

Refer to "Appendix B - Hex input conversion table" to convert rung input conditions to a hex code equivalent. Example 1 in figure 4.1 shows the ladder logic rewritten to repeat input C in each branch. Example 2 shows the ladder logic rewritten into four independent (parallel) branches. Follow these steps to convert to a hex equivalent:

- 1. Define all the inputs used in the first branch (ABCD). Referring to Appendix B, ABCD converts to 0F.

- 2. Define all the inputs used in the first branch that are low true logic (examine off). Input A is the only examine off. Referring to Appendix B, A converts to 01. Branch one (ABCD) then converts to 0F01.

$$\overline{A}BCD = 0F01$$

3. Define all the inputs used in the remaining three branches in the same way:

ĀBDF = 2B21 BCDE = 1E00 BDEF = 3A20

The following diagram shows the upper and lower bytes of the fourth independent branch of example 2 (BDE $\overline{F}$  = 3A20).

|                        |             |             | 1      | npu         | is us       | ed          |             |             |             | İng         |        |             |             | tru<br>off  |             | gic         |

|------------------------|-------------|-------------|--------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|--------|-------------|-------------|-------------|-------------|-------------|

| Bit                    | 17          | 16          | 15     | 14          | 13          | 12          | 11          | 10          | 07          | 06          | 05     | 04          | 03          | 02          | 01          | 00          |

| Input                  | 7<br>H<br>0 | 6<br>G<br>0 | 5<br>F | 4<br>E<br>1 | 3<br>D<br>1 | 2<br>C<br>0 | 1<br>B<br>1 | 0<br>A<br>0 | 7<br>H<br>0 | 6<br>G<br>0 | 5<br>F | 4<br>E<br>0 | 3<br>D<br>0 | 2<br>C<br>0 | 1<br>B<br>0 | 0<br>A<br>0 |

| Hex<br>Equi-<br>valent |             |             | 3      |             |             | Α           |             |             |             |             |        | 2           |             |             | 0           |             |

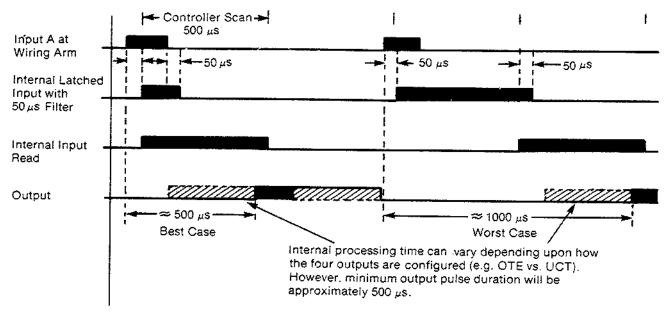

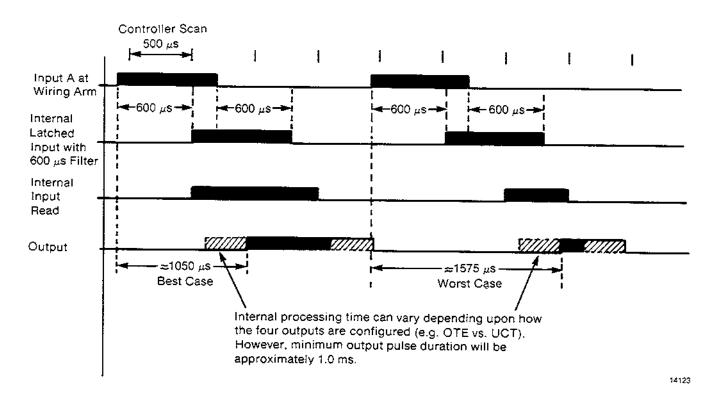

### Response time

You can select any time constant (50  $\mu s$  to 9999  $\mu s$ ) for controlling your module's response time. Refer to figures 4.2 and 4.3 for timing diagrams for 50  $\mu s$  and 600  $\mu s$  input filters. Response time is the time required to sense an input, process the data and control an output. Response times for some typical time constants are:

| Time constant     | Maximum Input frequency | Maximum response |

|-------------------|-------------------------|------------------|

| 50 μs             | 1000 Hz                 | 1.0 ms           |

| 100 µs - 499 µs   | 1000 Hz                 | 1.5 ms           |

| 2.0 ms - 2.499 ms | 200 Hz                  | 3.5 ms           |

| 4.5 ms - 4.999 ms | 100 Hz                  | 6.0 ms           |

| 7.0 ms - 7.499 ms | 67 Hz                   | 8.5 ms           |

| 9.5 ms - 9.999 ms | 50 Hz                   | 11.0 ms          |

Figure 4.2 Timing diagram for a 50 µs input filter

# Response time (continued)

Figure 4.3 Timing diagram for a 600 µs input filter

You select time constants by entering BCD numbers in storage words in the host processor's data table for transfer to the controller. You must assign the same time constant to pairs of inputs (0 and 1, 2 and 3, 4 and 5, 6 and 7). If an application requires less than 8 inputs, you must still allocate 5 words (one word for set input filter instruction 0300 and 4 words for input pairs) in the hex code file for input filter constants.

Following is the programming format in the hex code file for the input filters:

| Set input filler | 999                                      |

|------------------|------------------------------------------|

| Inputs 0 and 1   | 0050 (50 microseconds)                   |

| Inputs 2 and 3   | 1000 (one millisecond)                   |

| Inputs 4 and 5   | 9999 (9.999 milliseconds)                |

| Inputs 6 and 7   | 0000 (default value of 500 microseconds) |

# Response time

If no input filter value is entered at power-up the module will default to  $500~\mu s$ . Use this instruction only if you want to change from the  $500~\mu s$  default value.

WARNING: Up counter (UCT), down counter (DCT), counter reset (RCT), timer (TMR) and timer reset (TRS) instructions used with the I/O Logic Controller do not operate like the timers and counters associated with Allen-Bradley processors. Refer to figures 4.4, 4.5, 4.6 and the accompanying text for descriptions of operation.

# Up counter instruction (0013)

The up-counter instruction (UCT) increments its accumulated value for each false-to-true transition of an input branch (figure 4.4). Because only the false-to-true transition causes a count to be made, the input branch (rung condition) that has caused the accumulated value to increment by one must go from true-to-false before the next count is registered. When the accumulated value reaches the preset value, the output is turned on. UCT and DCT instructions for the same output must have the same preset and the same accumulated value programmed.

Unlike the timer instruction, the UCT instruction continues to increment its accumulated value after the preset value has been reached. If the accumulated value goes above 9999, it will roll to zero and, if the accumulated value is less than the preset, the output will de-energize.

# Up counter instruction (0013)

Figure 4.4

Functional diagram for an up-counter with reset

74120

# Counter reset instruction (0015)

The counter reset instruction (RCT) is an output instruction that resets the UCT or DCT accumulated count value to zero and de-energizes the output if its accumulated value is less then the preset value. If the preset is zero the output is always energized. In order for the counter to be reset, the RCT instruction must have the same output designation as the counter.

# Down counter instruction (0014)

The down-counter (DCT) instruction subtracts one from its accumulated value for each false-to-true transition of an input branch (figure 4.5). Because only the false-to-true transition causes a count to be made, the input branch (rung condition) that has caused the accumulated value to decrement by one must go from true-to-false before the next count is registered. The output energizes whenever the accumulated count equals or exceeds the preset value. If the accumulated value is less than the preset value, the output de-energizes. UCT and DCT instructions for the same output must have the same preset and the same accumulated value programmed.

Unlike the timer instruction, the DCT instruction continues to decrement its accumulated value after the preset has been reached. If the accumulated value goes below zero, it will roll to 9999, and if the accumulated value is greater than or equal to the preset, the output will energize. Normally, the down-counter instruction is paired with the up-counter instruction to form an up/down counter using the same output.

Figure 4.5

Functional diagram for a down-counter with reset

# Timer instruction (0017)

Use the timer instruction (TMR) to turn on a device oince a programmed time interval has timed out (figure 4.6). Once the input branch conditions make a false-to-true transition, the timer begins to count one millisecond time base intervals. The timer continues to count one millisecond time base intervals regardless of changing input branch conditions. The timer will only discontinue timing if it is reset by the (TRS) timer reset instruction. The accumulated time is reset at this time. The timer is re-enabled on the next false-to-true transition of its input condition (as long as the TRS is no longer true).

When the accumulated time equals the programmed preset time (1 ms to 10 seconds), the timer stops incrementing its accumulative time and energizes the output. If a false-to-true transition of the input occurs after the output has been energized, the output is de-energized and the accumulated time is reset to zero and begins timing again.

Figure 4.6 Functional diagram for a timer with reset

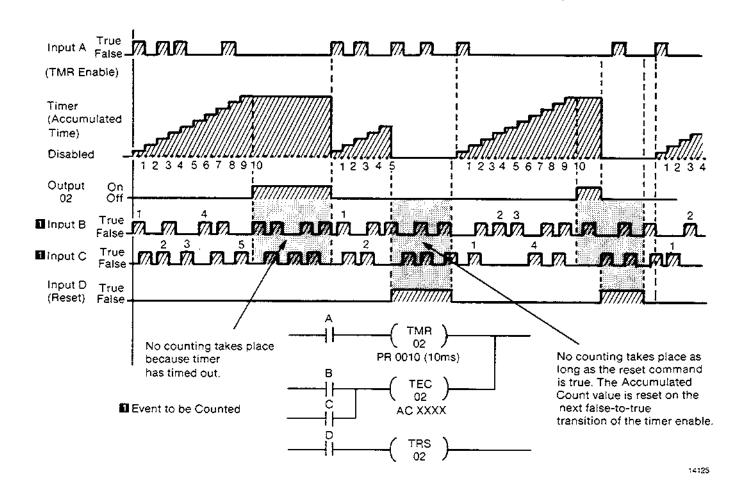

### Timed event counter instruction (0016)

The timed event counter (TEC) instruction (figure 4.7) counts events or pulses over a selected time interval while the timer is timing. This instruction is enabled when the input branch conditions make a false-to-true transition of the timer portion of the instruction. No counting takes place during the periods the timer is not timing. The timer will stop timing when it is reset by the timer reset (TRS) instruction. The accumulated time is reset at this time. The timer is re-enabled on the next false-to-true transition of its input condition as long as the reset condition is no longer true. When the accumulated time equals the preset time (1 ms to 10 seconds), the timer stops incrementing its accumulated time and energizes the output. If a false-to-true transition of the input occurs after the output is energized, the output de-energizes and the accumulated time resets to zero and begins timing again.

Figure 4.7 Functional diagram for a timed event counter with reset

# Timer reset instruction (0018)

The timer reset instruction (TRS) is an output instruction that resets the timer accumulated time to zero and de-energizes the output. In order for the timer to be reset, the TRS instruction must have the same output designation as the timer.

# Block-transfer-read data

Refer to figure 4.8 for the block-transfer-read data format.

Figure 4.8 Format of block-transfer-read data

| Bit<br>Word | 17                 | 16                 | 15             | 14           | 13      | 12            | 11    | 10              | 07       | 86   | 05       | 04      | 03       | <b>02</b> | 01    | 00       |

|-------------|--------------------|--------------------|----------------|--------------|---------|---------------|-------|-----------------|----------|------|----------|---------|----------|-----------|-------|----------|

| 1           | Power<br>Up        | Data<br>Valid      | Prog.<br>Error | H/W<br>Fault |         | Fuse<br>Blown |       | Boolean<br>Mode |          |      |          |         |          |           |       |          |

| 2           | 7                  | 6                  | 5              | Hardwa<br>4  | are Inp | uts<br>2      | 1     | 0               |          |      |          |         | На<br>3  | erdware   | Outpu | its<br>0 |

| 3           | Composite Inputs   |                    |                |              |         |               |       |                 |          |      | l        | .ogical | Output   | ŝ         |       | •        |

| 4           |                    |                    |                |              | Bina    | ıry value     | speci | fied with S     | ETID     | Comm | and      |         |          |           |       |          |

| 5           |                    | 80                 | CD             |              |         | C             | ount  |                 | Output 0 |      |          |         |          |           |       |          |

| 6           |                    | 80                 | CD             |              |         | C             | ount  |                 | Output 1 |      |          |         |          |           |       |          |

| 7           |                    | BCD Count Output 2 |                |              |         | 2             |       |                 |          |      |          |         |          |           |       |          |

| 8           | BCD Count          |                    |                |              |         |               |       | Output 3        |          |      |          |         |          |           |       |          |

| 9           | Error Word Pointer |                    |                |              |         |               |       |                 |          |      | Error    | Code    |          |           |       |          |

| 10          |                    | Comm               | unicati        | on Pro       | cessor  | Series/f      | ₹ev.  |                 |          | Co   | ntrol Pr | ocesso  | r Series | /Rev.     |       |          |

### Word 1 - Status flags

The first status word contains the status flags in the upper byte and zeroes in the lower byte.

| Word | Bit | Description                                                                                                                                                                                                                |

|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | 10  | When set to one, the Boolean Mode bit indicates that the programming format is in terms of ladder logic expressions.                                                                                                       |

| 1    | 12  | When set to one, the fuse blown bit indicates that one or more of the 3A rectifier fuses protecting the output circuitry has blown.                                                                                        |

| 1    | 14  | When set to one, the hardware fault bit indicates that the controller has a hardware problem.                                                                                                                              |

| 1    | 15  | When set to one, the program error bit indicates that a program error in the hex file transferred to the controller has occurred. This bit remains set until an INIT command is received or power to the rack is recycled. |

| 1    | 16  | When set to one, the data valid bit indicates that the data transferred to the controller using block-transfer is valid (no program errors).                                                                               |

| 1    | 17  | When set to one, it indicates that the controller has passed its power up diagnostics routine and is ready to receive a program.                                                                                           |

### Word 2 - Hardware outputs and inputs

Word 2, bits 00 through 03 represent the state of outputs 0 through 3. When set to one, the bit indicates that the output at the corresponding terminal on the 1771-WG wiring arm is supplying voltage to the device.

When reset to zero, the bit indicates that the output at the corresponding terminal on the 1771-WG wiring arm is not supplying voltage to the device. Refer to figure 4.9 - I/O Block diagram.

Word 2, bits 10 through 17 represent the state of inputs 0 through 7. When set to one, the bit indicates that the input is true (10 to 24 V at the corresponding terminal on the 1771-WGwiring arm). When reset to zero, the bit indicates that the input is false (0 to 4 V at the corresponding terminal on the 1771-WG wiring arm).

### Word 3 - Logical outputs and composite inputs

Word 3, bits 00 through 03 represent the logical state of outputs 0 through 3 without being conditioned by the Disable output command and/or the Force output command. Refer to Figure 4.9 - I/O Block diagram.

Figure 4.9 I/O block diagram

### Word 3 - Logical outputs and composite inouts (continued)

When set to one, the bit indicates that the logic equation of the output is true. When reset to zero, the bit indicates that the logic equation of the output is false.

Word 3, bits 10 through 17 represent the logical state of inputs used in the logic equations.

When set to one, the bit indicates that the input will be used in the logic equations as high true logic (on). When reset to zero, the bit indicates that the input will be used in the logic equations as low true logic (off).

### Word 4 - Binary value specified with SETID command

Use SETID (0004) when you need more than 64 words for your program. The address is returned in the fourth status word and is used to link multiple block-transfers if more than 64 words are required. Also use this command as a block identifier in the configuration file. This helps you to identify which program within the file you are currently using.

### Words 5, 6, 7 and 8 -Binary coded decimal (BCD) counts

Use words 5 through 8 for BCD counts when outputs 0, 1, 2 and 3 are defined as up counter (UCT), down counter (DCT) or timed event counter (TEC) instructions. The value of the accumulated count (max 9999) is returned to the processor.

- Word 5 = BCD count for output 0

- Word 6 = BCD count for output 1

- Word 7 = BCD count for output 2

- Word 8 = BCD count for output 3

### Word 9 - Error code and error word pointer

Word 9, bits 10 through 17 (error word pointer) points to the word in the hex file where a programming error has occurred.

Word 9, bits 00 through 07 (error code) specifies what type of programming error has occurred. Refer to the following section titled "Programming errors".

Word 10 - Control processor series/revision and Communication processor series/revision

Word 10, bits 00 through 07 specifies the current series/revision of the control processor on the controller module.

|        | Control Process | <b>or</b>            |

|--------|-----------------|----------------------|

| Series | Revision        | Hex code             |

| Α      | Α               | 21<br>22<br>23<br>24 |

| Α      | В               | 22                   |

| Α      | С               | 23                   |

| Α      | Ð               | 24                   |

| В      | Α               | 41                   |

| В      | В               | 42                   |

| В      | C               | 42<br>43             |

| В      | ٥               | 44                   |

Word 10, bits 10 through 17 specifies the current series/revision of the communication processor on the controller module.

| Coi    | nmunication Pro | cessor   |

|--------|-----------------|----------|

| Series | Revision        | Hex code |

| Α      | Α               | 21       |

| Ι Α    | В               | 22       |

| A      | С               | 23<br>24 |

| A      | D               | 24       |

| В      | Α               | 41       |

| В      | В               | 42       |

| В      | C               | 43       |

| 8      | D               | 44       |

The value 2121 in status word 10 indicates series A and revision A for both the control and communication processors.

# Programming example

The following programming example shows the various output commands, hex codes and associated ladder logic:

| Parameter                                                                                    | Hex code                                             | Equivalent toddir folic                                                               |

|----------------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------|

| Initialize                                                                                   | 0001                                                 |                                                                                       |

| UCT Output 0 Preset Accumulated Input branch Input branch Input branch                       | 0013<br>FF00<br>1000<br>0850<br>C707<br>8880<br>3830 | A B C G H  [1/{}/{}/{}] [] [(UCT)-]  D H   000  [] {}/{                               |

| DCT Output 0 Preset Accumulated Input branch Input branch                                    | 0014<br>FF00<br>1000<br>0850<br>7A00<br>C040         | B D E F G   ) [] [] [] [ (OCT)-    G H                                                |

| RCT<br>Output 0<br>Input branch                                                              | 0015<br>FF00<br>0100                                 | A<br>[] [(RCT)-[,                                                                     |

| OTE<br>Output 1<br>Input branch                                                              | 0010<br>FF01<br>5744                                 | A B C E G   13 (3 (3 (3 (3 (3 (3 (3                                                   |

| OTL Output 2 Input branch Input branch                                                       | 0011<br>FF02<br>4B40<br>1000                         | A B D G  [] () () () ((L)-   E   02  [] (                                             |

| OTU<br>Output 2<br>Input branch                                                              | 0012<br>FF02<br>1818                                 | D E  }/[]/[( U )-                                                                     |

| TMR Output 3 Time Input branch                                                               | 0017<br>FF03<br>9125<br>8181                         | A H<br> ]/[]/{(TMR)- <br>03<br>timer:<br>9.125                                        |

| TEC<br>Output 3<br>Input branch<br>Input branch                                              | 0016<br>FF03<br>2E02<br>4E02                         | B C D F<br> ]/() () (                                                                 |

| TRS Output 3 Input branch                                                                    | 0018<br>FF03<br>8000                                 | H<br> ] {(TR\$)- <br>03                                                               |

| Set input<br>filters<br>Inputs 0 and 1<br>Inputs 2 and 3<br>Inputs 4 and 5<br>Inputs 6 and 7 | 0030<br>0000<br>9999<br>0850<br>2500                 | default value of 500 us<br>9.999 milliseconds<br>850 microseconds<br>2.5 milliseconds |

| Execute                                                                                      | 0003                                                 |                                                                                       |

| Total words in hex file<br>Maximum allowable file len                                        | ath                                                  | 44 words<br>64 words                                                                  |

|                                                                                              | 3                                                    | 01779100                                                                              |

#### Programming errors

Word 1, bit 15 (program error status bit) of the read block transfer file is set if any program errors exist in the hex file that is transferred to the controller.

Word 9, bits 00 through 07 inform you of the type of problem. Bits 10 through 17 point to the incorrect word in the hex file.

If an error occurs during programming, the Execute Command (0003) is not processed and all outputs are deenergized. Additional commands are not accepted until an Initialized Command (0001) is processed. If a program is executing when a command generates an error, the program will halt execution and all outputs are de-energized.

#### Programming boundaries

You can assign the same output address to any one of the following groups of similar instructions without having a programming error occur (Table 4-1). For example, you can assign the same output address to each of three rungs whose outputs are an up counter (UCT), down counter (DCT) and reset counter (RCT) and another output address to each of two rungs whose outputs are latch (L) and unlatch (U) without causing a programming error. However, if you define an output as an up counter (UCT) and as a latch (L) a programming error occurs. The module sets an error bit and stops operating when it detects a programming error.

You can use any one of four output addresses, 00-03, to define a rung. The maximum number of rungs of equivalent ladder logic can vary from four (using only output energize instructions) to twelve (using only counter instructions). You can assign the same output address to any of the groups in table 4-1, only once.

Table 4-1 Programming boundaries

|  | -( )- | -(L)-<br>-(U)- | -(UCT)-<br>-(DCT)-<br>-(RCT)- | -(TMR)-<br>-(TRS)- | -(TMR)-(TEC)-<br>-(TRS)- |

|--|-------|----------------|-------------------------------|--------------------|--------------------------|

|--|-------|----------------|-------------------------------|--------------------|--------------------------|

Following is a list of possible errors and their associated error codes which are displayed in the lower byte of the ninth status word (refer to figure 4.8):

| Error code | Error                                                                                                                                                                  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01         | You assigned an invalid output command. A valid command has an upper byte of zeroes. The lower byte must be a valid BCD number which is an output command.             |

| 02         | Program error. Command must fit within block-transfer file length.                                                                                                     |

| 03         | You entered an output again as the same function or as a different function outside of the programming boundaries. Refer to Table 4-1,"Programming boundaries", above. |

| 04         | You entered a command other than an on-line command after the Execute Command (0003), to program an output.                                                            |

| 05         | Invalid command                                                                                                                                                        |

| 07         | Incorrect upper byte for this command.                                                                                                                                 |

| 08         | You assigned an invalid output address.                                                                                                                                |

| 09         | Invalid command                                                                                                                                                        |

| 10         | This word contains an invalid BCD digit.                                                                                                                               |

| 11         | You must assign the same preset and accumulated values to UCT and DCT instructions having the same address.                                                            |

| 12         | You assigned an invalid fifter time constant.                                                                                                                          |

| 13         | Invalid command                                                                                                                                                        |

| 14         | Invalid command                                                                                                                                                        |

| 15         | Invalid command                                                                                                                                                        |

| 16         | Invalid command                                                                                                                                                        |

| 17         | Invalid command                                                                                                                                                        |

| 18         | Invalid command                                                                                                                                                        |

#### Commands

There are two types of commands in your controller instruction set.

- Configuration data commands

- On-line commands

#### Commands (continued)

Use the configuration data commands to initially configure or program the controller. You can use all the controller's commands as configuration data commands. Use the on-line commands to change your program after it has been block-transferred to the controller. You can do this without causing any program errors or impeding I/O processing. Following is a list of the configuration data and on-line commands and their hex codes.

| Configuration data c | ommands |

|----------------------|---------|

| NOP                  | (0000)  |

| INIT                 | (0001)  |

| HALT                 | (0002)  |

| EXEC                 | (0003)  |

| SETID                | (0004)  |

| END                  | (0005)  |

| OTE                  | (0010)  |

| OTL                  | (0011)  |

| OTU                  | (0012)  |

| UCT                  | (0013)  |

| DCT                  | (0014)  |

| RCT                  | (0015)  |

| TEC                  | (0016)  |

| TMR                  | (0017)  |

| TRS                  | (0018)  |

| SETIF                | (0030)  |

| DISABLE OUTPUT       | (0031)  |

| FORCE OUTPUT         | (0032)  |

| MASK INPUT           | (0033)  |

| Ön-line comma  | ınds   |

|----------------|--------|

| NOP            | (0000) |

| HALT           | (0002) |

| EXEC           | (0003) |

| SETID          | (0004) |

| END            | (0005) |

| DISABLE OUTPUT | (0031) |

| FORCE OUTPUT   | (0032) |

| MASK INPUT     | (0033) |

## Configuration data commands

The following configuration data commands are described under "Output instructions" earlier in this section:

| OTE | (0010) | RCT | (0015) |

|-----|--------|-----|--------|

| OTL | (0011) | TEC | (0016) |

| OTU | (0012) | TMR | (0017) |

| UCT | (0013) | TRS | (0018) |

| DCT | (0014) |     | (+ /   |

4-24

#### Configuration data commands (continued)

Following is a list of the remaining configuration data commands:

NOP (0000) - Reserves one word in the hex file for adding an instruction to the file at a later date without changing the values in the rest of the file. This command can also edit or eliminate current logic that may no longer be required.

INIT (0001) - Clears out the present controller program and sets all parameters to the default state. It also stops all I/O processing and de-energizes all outputs.

HALT (0002) - Use this command to immediately stop all I/O processing. Outputs remain in their last state regardless of the input conditions. An Execute Command (0003) must be sent to the module to resume I/O processing.

EXEC (0003) - Normally follows reconfiguration data and causes the module to begin execution of the most recent program downloaded from the processor. It also stops processing of any remaining data in the block-transfer data block.

SETID (0004) - This command when processed by the controller returns a BCD or binary value in the fourth status word of the block-transfer-read. You need additional ladder logic to pass this value from the fourth status word to the block-transfer-write file address. You can also use this command as a block identifier in the configuration file to help you identify which program is in current use when you are using multiple programs. Also use this command to link multiple block-transfers together if more than 64 words are required to define a program. The SETID command uses the following programming format:

0004 SETID Command XXXX Address value

END (0005) - Module executes the program up to but not beyond the END instruction. You can use this command to debug parts of your program without executing the complete program. All words following this command are not processed by the module including the Execute Command (0003).

SETIF (0030) - Provides the means to change the input filter constant for a given input pair. Four data words follow this command to allow you to program individual filter constants (one word for each input pair).

# Configuration data commands (continued)

Disable Outputs (0031) - You can use this command during installation to verify operation of the module without requiring connections to output devices. The output of the logic equations is verified in the status block (word 3). Use the mask input command with the disable output command to provide inputs to the logic equations. This means you do not need an actual hardwired input device. The disable output command disables selected outputs and controls the outputs regardless of the state of the input conditions. In the default condition all outputs are enabled. The disable output command uses the following programming format:

0031 FF0X

Disable Output Command

Where X is the hex code for the outputs that are

disabled

| Hex                        | Disabled Outputs |

|----------------------------|------------------|

| F                          | None             |

| E<br>D<br>C<br>B<br>A<br>9 | [ 0              |

| D                          | 1                |

| C                          | 0,1              |

| В                          | 2<br>0,2         |

| A                          | 0,2              |

|                            | 1,2              |

| 8                          | 0,1,2            |

| 7                          | 3                |

| 6<br>5                     | 0,3              |

| 5                          | 1,3              |

| 4<br>3                     | 0,1,3            |

| 3                          | 2,3              |

| 2                          | 0,2,3            |

|                            | 1,2,3            |

| 0                          | 0,1,2,3          |

Force Output (0032) - Use the force output command during initial installation to verify proper operation of an output device. You can use this command at any time (before a valid configuration file) as long as no program errors exist. The force output command forces the selected outputs on or off overriding any other status. It uses the following programming format:

0032 0X0X Force Output Command

Where X in the upper byte selects the output or combination of outputs to be forced.

Where X in the lower byte selects whether the output or combination of outputs are forced ON or OFF.

Use 0000 to unforce all commands.

#### Configuration data commands (continued)

|          | per Byte<br>to be forced) |          | Lower By<br>(ON/OFI | tie<br>7)      |

|----------|---------------------------|----------|---------------------|----------------|

| Hex Code | Outputs                   | Hex Code | Outputs<br>ON       | Outputs<br>OFF |

| 0        | None                      | lo       | None                | 0,1,2,3        |

| 1        | 0                         | 1        | 0                   | 1,2,3          |

| 2        | 1                         | 2        | 1                   | 0,2,3          |

| 3        | 0,1                       | 3        | 0,1                 | 2,3            |

| 4        | 2                         | 4        | 2                   | 0,1,3          |

| 5<br>6   | 0,2                       | 5        | 0,2                 | 1,3            |

| 6        | 1,2                       | 6        | 1,2                 | 0,3            |

| 7        | 0,1,2                     | 7        | 0,1,2               | 3              |

| 8        | 3                         | 8        | 3                   | 0,1,2          |

| 9        | 0,3                       | 9        | 0,3                 | 1,2            |

| Α        | 1,3                       | A        | 1,3                 | 0,2            |

| B        | 0,1,3                     | В        | 0,1,3               | 2              |

| С        | 2,3                       | C        | 2,3                 | 0,1            |

| D        | 0,2,3                     | D        | 0,2,3               | 1              |

| E<br>F   | 1,2,3                     | E        | 1,2,3               | 0              |

| F        | 0,1,2,3                   | F        | 0,1,2,3             | None           |

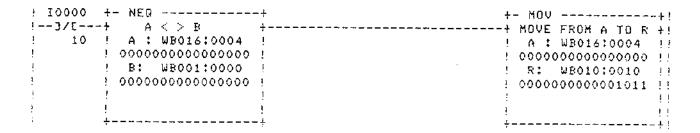

Mask Inputs (0033) - Masks selected inputs from the wiring arm so the processor can substitute programmed bits. Use the Mask Input Command when an input from the processor is required for an enable or interlock. The Initialize Command (0001) sets the default to have all inputs coming from the wiring arm. Once an input is programmed to come from the processor data table, it remains that way until a new Initialize Command is entered or a new Mask Input Command is entered.

Use of the Mask Input Command changes the overall system response time due to processor scan time, block-transfer time etc. Refer to Appendix A for examples of block-transfer timing. The Mask Input Command uses the following programming format:

0033 Mask Inputs Command

XXYY XX in the upper byte selects which inputs are coming from the processor data table. Refer to Appendix B - Hex Input Conversion Table for the appropriate hex code.

> YY in the lower byte selects the logical value of the inputs used in the logic equations.

# Configuration data commands (continued)

#### Example:

|                                                                                   | Inp    |        |        |               | roce<br>/te) |                           | ME.                            |               |                |     |        | ical<br>ver |          |        |    | <b>X</b> |               |

|-----------------------------------------------------------------------------------|--------|--------|--------|---------------|--------------|---------------------------|--------------------------------|---------------|----------------|-----|--------|-------------|----------|--------|----|----------|---------------|

| BIt                                                                               | 17     | 16     | 15     | 14            | 13           | 12                        | 11                             | 10            | Bit            | 07  | 06     | 05          | 04       | 03     | 02 | 01       | 80            |

| Input<br>Mask                                                                     | 7<br>0 | 6<br>0 | 5<br>0 | <u>4</u><br>1 | 3<br>0       | 2                         | †<br>0                         | <u>0</u><br>1 | Input<br>Logic | 7   | 6<br>0 | 5<br>0      | <u>4</u> | 3<br>0 | 2  | 1        | <u>0</u><br>1 |

| Hex<br>Equi-<br>valent                                                            |        | 1      |        |               |              | 1                         |                                |               |                |     | 0      |             |          |        | 1  | •        |               |

| A (1) in each Mask field selects that input to originate from the host processor. |        |        |        |               |              |                           | A (1) ir<br>that the<br>proces | e inpu        | ıt fr          | om  | the    | hos         |          | ates   | •  |          |               |

| A (0) in each Mask field selects that input to originate from the wiring arm.     |        |        |        |               |              | A (0) in that the process | e inpu                         | it fr         | om             | the | hos    |             | ates     | •      |    |          |               |

In our example above inputs 0 and 4 (underlined) come from the processor. Input 0 is true (on) and input 4 is false (off).

#### On-line commands

The following configuration data commands are also on-line commands. Refer to the descriptions above found under "Configuration data commands".

| END            |

|----------------|

| DISABLE OUTPUT |

| FORCE OUTPUT   |

| MASK INPUT     |

|                |

Mask input programming examples for PLC-2 and PLC-3 family processors

The following examples show how to use the mask input feature and the associated ladder logic.

This mask input example uses two data files. The first data file contains the configuration data to program the controller. The second data file contains the mask input command and the end of program command.

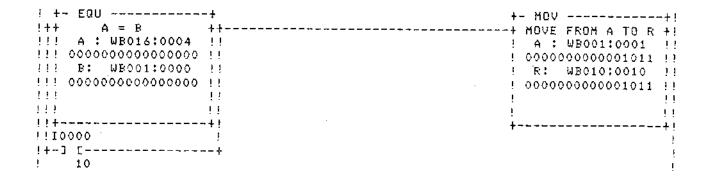

#### PLC-2 family processors

Controller logic

Inputs A (0) and E (4) come from inputs connected to the host processor located in rack 1, module group 2, terminal 1 and rack 1, module group 2 and terminal 2, respectively.

| Parameter                                                                                  | Hex Code                                                     | Octal Address<br>in PLC-2 processor                  |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------|

| Initialize OTE Output 1 Input branch Input branch Mask Input Inputs from processor Execute | 0001<br>0010<br>FF01<br>0F09<br>F060<br>0033<br>1101<br>0003 | 224<br>225<br>226<br>227<br>230<br>231<br>232<br>233 |

| Mask Input<br>Inputs from processor<br>End of program                                      | 0033<br>1110<br>0005                                         | 400 On-line<br>401 data file<br>402                  |

#### PLC-2 family processors (continued)

The following support logic in a PLC-2 processor will perform the mask input example.

```

LADDER DIAGRAM DUMP

START

! 150

131

Rung 1 +- [6]-

! 400

224

! Data Power-

valid up

bit bit

! 212 212 151

131

Rung 2 +- ]/[---] [-+-[G]----

! 16 17! 224

224

! Pushbutton !

to load !

new program!

112

+-] [----+

0.0

Read Write

done enable

! 110

010

+-----+ 010

07

!DATA ADDR: 030! 07

100!

!MODULE ADDR:

!BLOCK LENGTH:

Read

(FILE: 200- 211+--(DN)--+

done

! 110 Buffer file

+----+ 034

Rung 4 +-2 [----+ FILE TO FILE MOVE+--(ER)--+

0.7

!COUNTER ADDR: 034! 17 !

!POSITION: 001!

!FILE LENGTH: 010! 034

!FILE A: 200- 211+--(DN)--!

!FILE R: 212- 223! 15 !

!Write Read

!done enable

!RATE PER SCAN: 010!

110 010

t-----+ 010

! 06 07

!BATA ADDR: 031! 06 !

!MODULE ADDR: 100!

08! 110

!BLOCK LENGTH:

!FILE: 224- 233+--(DN)--+

! 112

______( )--+

Rung 6 +- ] [--

01

1 112

401

Rung 7+-3/[-----()--+

. 02

04 !

```

#### Rung descriptions for mask input PLC-2 family processor example program

- Rung 1 Unconditionally loads the mask input data file starting address into the block-transfer-write (BTW) instruction. Length of the file must not exceed the BTW length.

- Rung 2 Configuration file starting address is loaded into the BTW instruction conditioned by the power-up bit (212/17) being true and the data-valid bit (212/16) being false or a pushbutton being on.

- Rung 3 Both the read done bit (110/07) and write enable bit (010/06) being false are used to condition the block-transfer-read (BTR) so that different block lengths for reads and writes can be used.

- Rung 4 Use a file-to-file move to buffer the read data when making any data comparisons.

- Rung 5 Both the write done bit (110/06) and read enable bit (010/07) being false are used to condition the BTW so that different block lengths for reads and writes can be used.

- Rung 6 Used for Mask Input Command. Input (112/01) is used to condition bit 401/00 (Input 0) which is passed from the host processor.

- Rung 7 Used for Mask Input Command. Input (112/02) is used to condition bit 401/04 (Input 4) which is passed from the host processor.

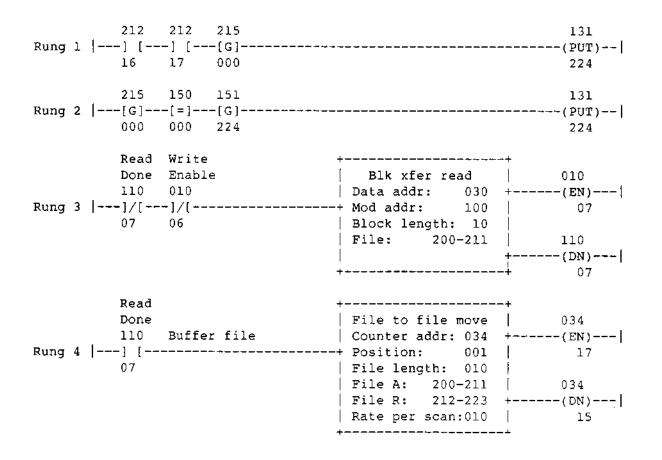

### PLC-3 family processors

Controller logic

### PLC-3 family processors (continued)

Inputs A (0) and E (4) come from the host PLC-3 processor rack 0, module group 0, terminal 7 and rack 0, module group 0 and terminal 6, respectively.

| Parameter         | Hex Code | Addres   | s in PLC-3  |

|-------------------|----------|----------|-------------|

| Initialize        | 0001     | B15:11 ) |             |

| OTE               | 0010     | B15:12   |             |

| Output 1          | FF01     | B15:13   |             |

| Input branch      | 0F09     | B15:14   | Config-     |